# Grundlagen der Technischen Informatik 2

#### Digitaltechnik Rechneraufbau

Prof. Dr. U. Kebschull Technische Informatik kebschull@informatik.uni-leipzig.de

Technische Informatik 2 Stand SS 01 U. Kebschull

#### Übersicht

- **O** Einleitung

- Schaltnetze

- **⇒** KV-Diagramme

- **⇒ Minimierung nach Quine MC-Cluskey**

- **⇒** Bündelminimierung mit KV-Diagrammen

- Speicherglieder

- **⇒** RS-Flipflop

- **⇒** D-Flipflop

- **⇒** JK-Flipflop

- **⇒** T-Flipflop

#### Übersicht

- Schaltwerke

- **⇒** Darstellung endlicher Automaten

- **⇒** Minimierung der Zustandszahl

- **⇒** Einfluss der Zustandskodierung

- Spezielle Schaltnetze und Schaltwerke

- ⇒ Multiplexer, Demultiplexer, Addierer

- ⇒ Register, Schieberegister, Zähler

- Rechnerarithmetik

- **⇒** Formale Grundlagen

- **⇒** Addition und Subtraktion

- **⇒** Multiplikation und Division

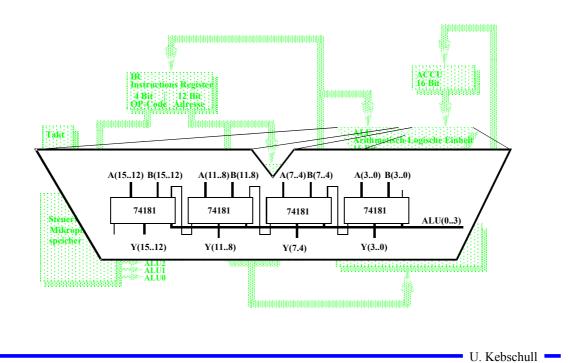

- ⇒ Arithmetisch-Logische Einheit (ALU)

U. Kebschull

Technische Informatik 2

Stand SS 01

2

# Übersicht

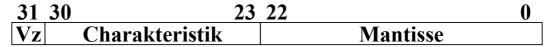

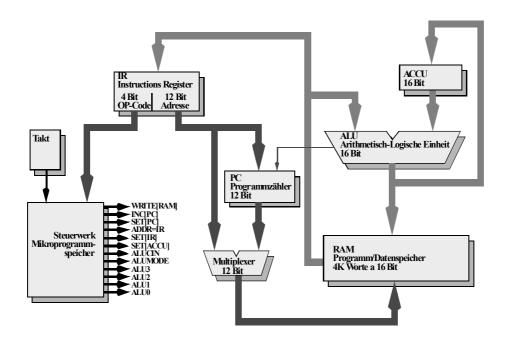

- O Ein minimaler Rechner

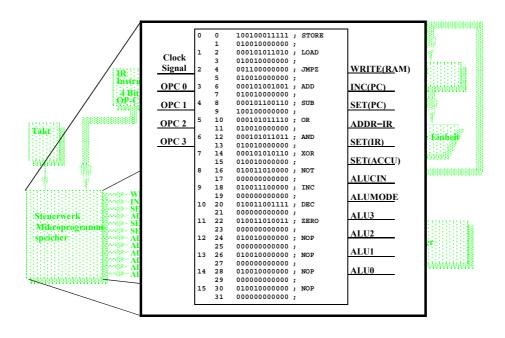

- **⇒** Befehlssatz

- **⇒** Realisierung

- **⇒** Arbeitsweise und Programmierung

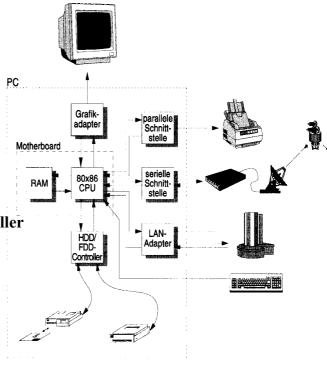

- Aufbau von Rechnersystemen

- **⇒** Komponenten eines Rechnersystems

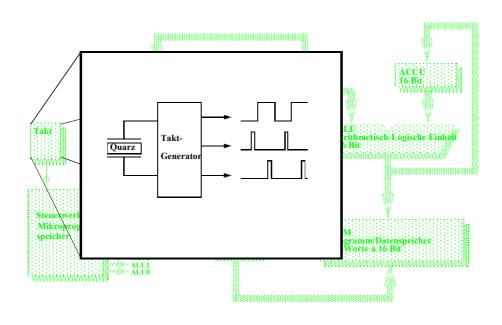

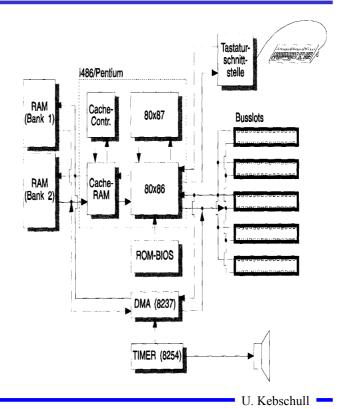

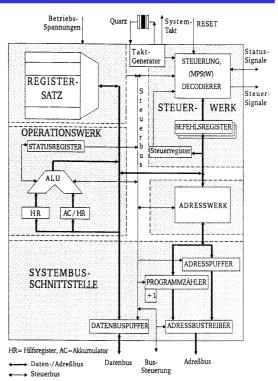

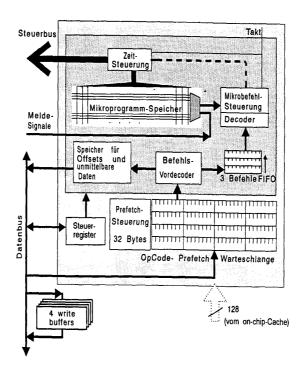

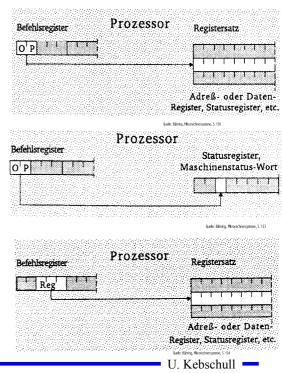

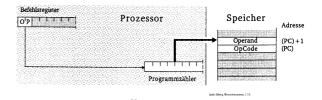

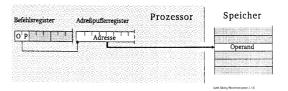

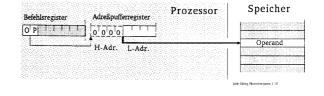

- Prinzipieller Aufbau eines Mikroprozessors

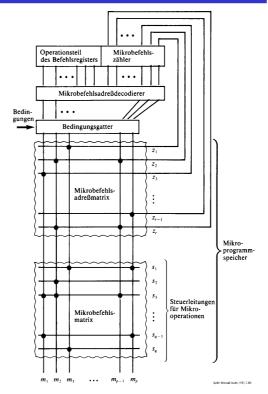

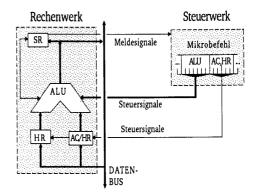

- **⇒** Steuerwerk und Mikroprogrammierung

- **⇒** Rechenwerk

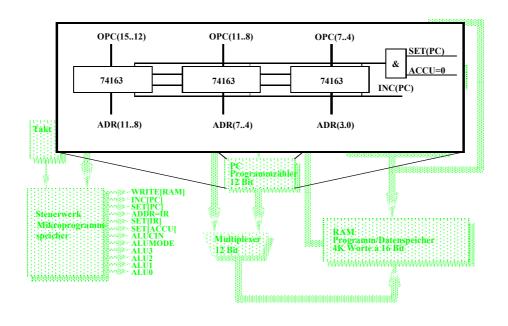

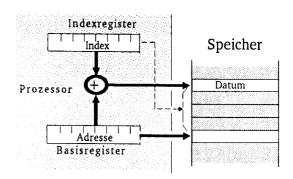

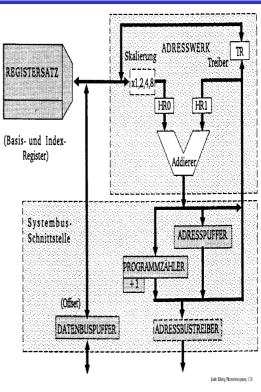

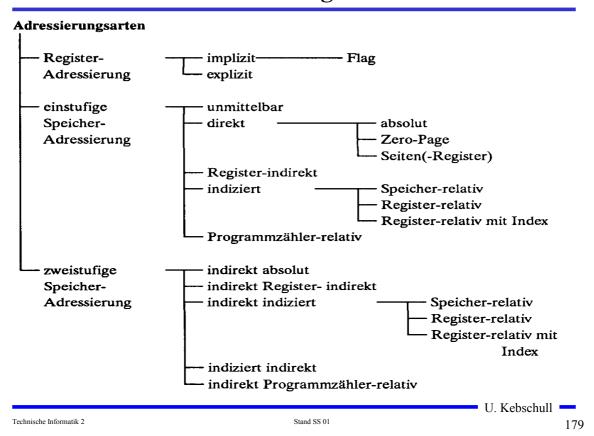

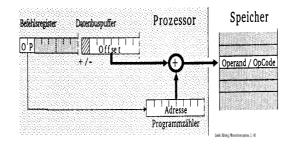

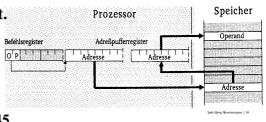

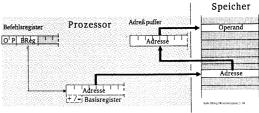

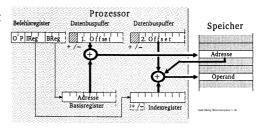

- **⇒** Das Adresswerk

#### Übersicht

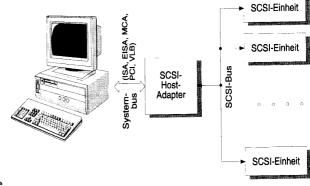

- O Rechner- und Gerätebusse

- **⇒** interne Busse

- **⇒** externe Busse

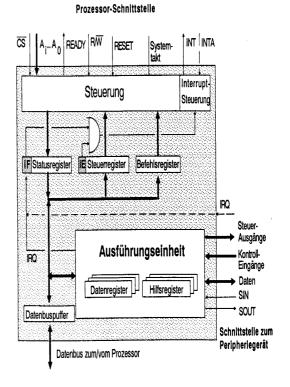

- **○** E/A-Steuerungen

- ⇒ Prinzip der Datenein-und -ausgabe

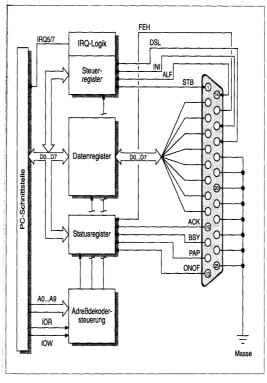

- **⇒** Parallele Schnittstellen

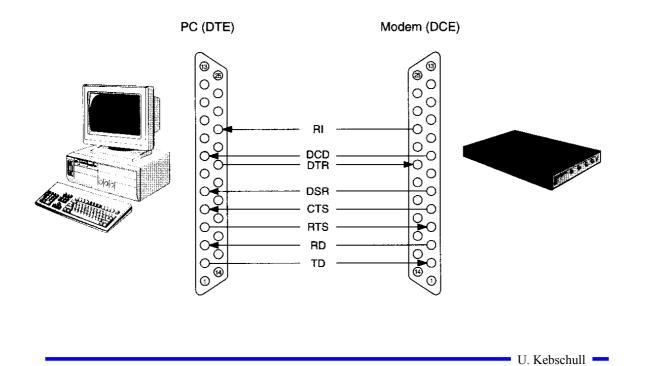

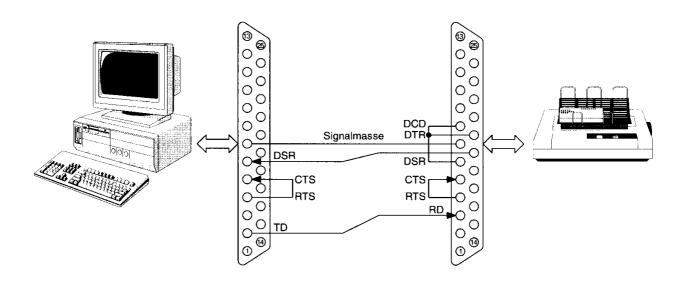

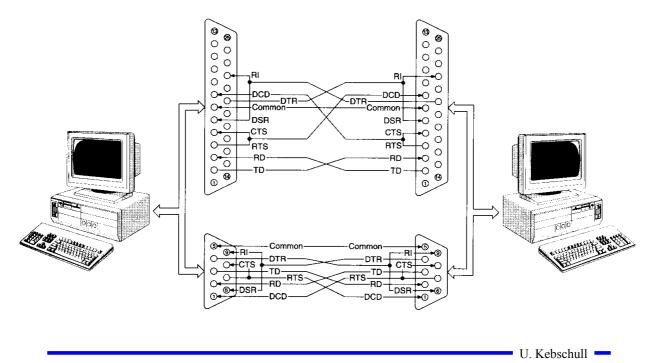

- **⇒** Serielle Schnittstellen

- **⇒** Analoge Ein- und Ausgabe

- Peripheriegeräte

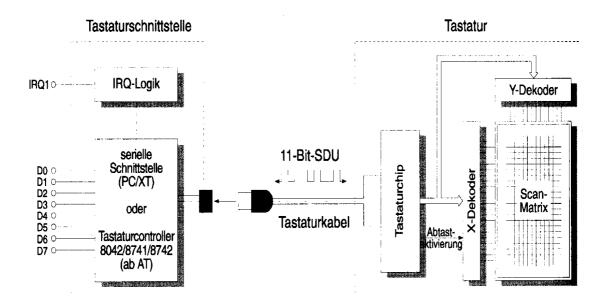

- **⇒** Tastatur

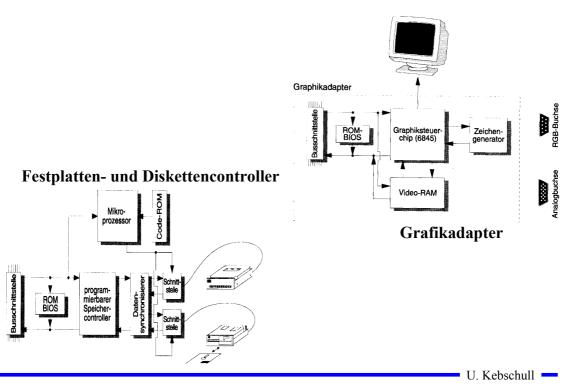

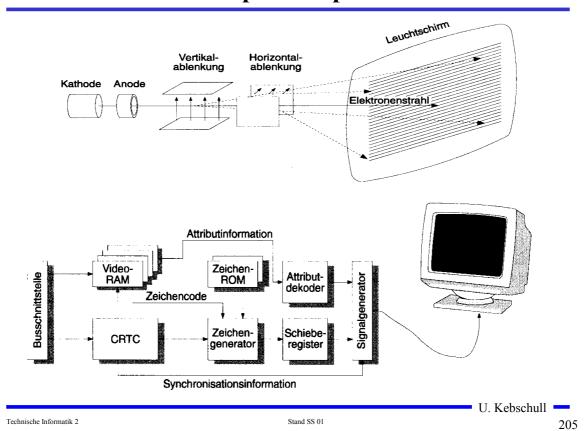

- **⇒** Graphikadapter

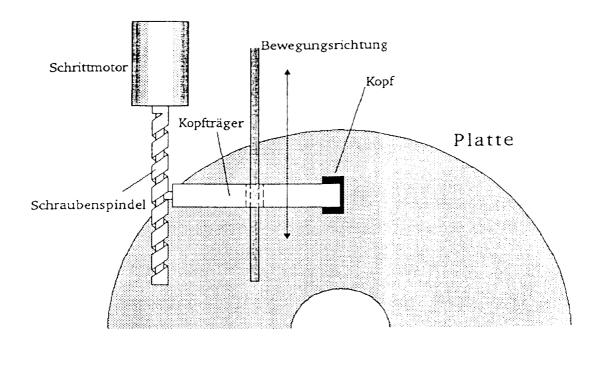

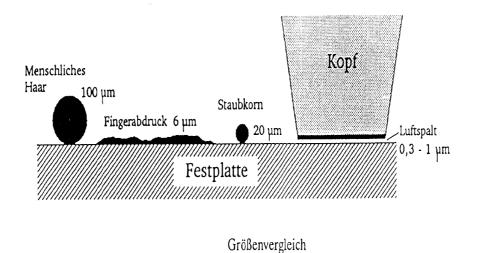

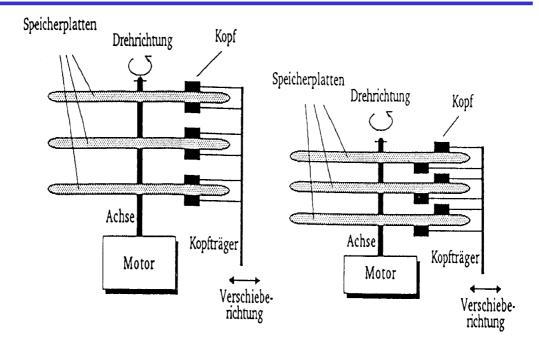

- **⇒** Festplatten- und Diskettenlaufwerke

- **⇒** Sonstige E/A-Geräte

U. Kebschull

Technische Informatik 2

Stand SS 01

5

#### Literatur

#### Die Vorlesung basiert auf den Lehrbüchern:

- W. Schiffmann, R. Schmitz: "Technische Informatik 1 Grundlagen der digitalen Elektronik"

Springer-Lehrbuch, Springer-Verlag (1992)

- W. Schiffmann, R. Schmitz: "Technische Informatik 2 Grundlagen der Computertechnik"

Springer-Lehrbuch, Springer-Verlag (1992)

- O H. Bähring: "Mikrorechnersysteme" Springer Lehrbuch, Springer-Verlag (1994)

#### 0 Einleitung

Der Entwurf elektronischer Systeme ist gekennzeichnet durch:

- **Q** Zunahme der Komplexität und Integrationsdichte

- O höhere Packungsdichten aufgrund geringerer Strukturgrößen

- steigende Anforderungen (Platzbedarf, Taktrate, Leistungsverbrauch, Zuverlässigkeit)

- **O** kurze Entwicklungszeiten (time to market)

- **O** Wiederverwendung von Entwurfsdaten (Re-use)

- Die Entwicklung elektronischer Systeme ist bei der heutigen Komplexität nur durch eine strukturierte Vorgehensweise beherrschbar!

U. Kebschull

Technische Informatik 2

Stand SS 01

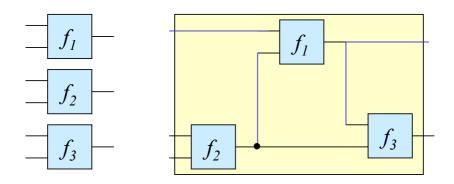

#### Grundprinzip des Entwurfs

Komponenten + Struktur = gewünschtes Verhalten

Technische Informatik 2 Stand SS 01

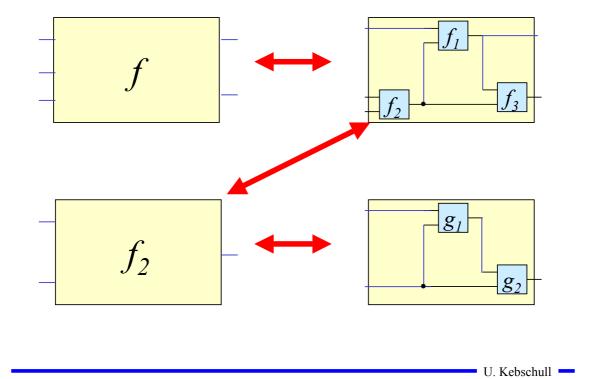

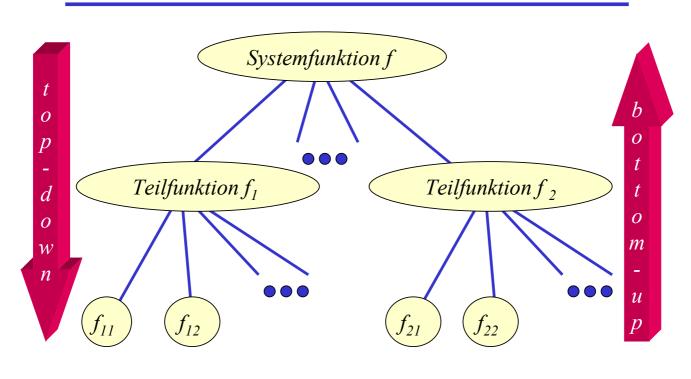

# **Abstraktion und Detaillierung**

Technische Informatik 2 Stand SS 01

# "top-down" und "bottom-up"

Technische Informatik 2 Stand SS 01 10

#### Technische Kriterien für den Entwurf von Schaltnetzen

- O Korrekte Realisierung unter Beachtung des statischen und dynamischen Verhaltens der verwendeten Bauelemente

- O Berücksichtigung technischer Beschränkungen (Anzahl der Eingänge, begrenzte Belastbarkeit der Ausgänge, zur Verfügung stehende Bausteine (Bausteinbibliothek), Temperaturgrenzen, Speicherplatz (bei PLAs), Taktfrequenz)

- O Gewährleistung hoher Systemzuverlässigkeit (leichte Testbarkeit, Selbsttest, Fehlertoleranz, zuverlässiger Betrieb)

- O Berücksichtigung von Forderungen an die Gebrauchseigenschaften (universelle Einsatzmöglichkeit, großer Funktionsumfang)

- O Berücksichtigung technologischer Nebenbedingungen (Kühlung, Versorgungsspannung)

- O Vermeidung von Störeinflüssen (elektromagnetische Felder)

Technische Informatik 2 Stand SS 01 U. Kebschull

#### Ökonomische Kriterien für den Entwurf von Schaltnetzen

- O Geringe Kosten für den Entwurf (Entwurfsaufwand)

- **⇒** Lohnkosten

- **⇒** Rechnerbenutzung, Softwarelizenzen

- O Geringe Kosten für die Realisierung (Realisierungsaufwand)

- **⇒** Bauelemente, Gehäuseformen

- O Geringe Kosten für die Inbetriebnahme

- ⇒ Kosten für den Test

- ⇒ Fertigstellung programmierbarer Bauelemente

- O Geringe Kosten für den Betrieb

- **⇒** Wartung

- **⇒** Stromverbrauch

#### Entwurfsziele

- Manche Kriterien stehen im Widerspruch

- ⇒ zuverlässigere Schaltungen erfordern einen höheren Realisierungsaufwand

- ⇒ Verringerung des Realisierungsaufwand erfordert eine Erhöhung der Entwurfskosten

- O Ziel des Entwurfs ist das Finden des günstigsten Kompromisses aus

- **⇒** Korrektheit der Realisierung

- **⇒** Einhaltung der technologischen Grenzen

- ⇒ ökonomische Kriterien

- Wir betrachten in dieser Vorlesung nur die Minimierung des Realisierungsaufwands

Technische Informatik 2 Stand SS 01 U. Kebschull

13

# 1 Minimierungsverfahren

- Finden von Minimalformen Boolescher Funktionen

- ⇒ ohne Betrachtung der Zieltechnologie

- ightharpoonup mit Betrachtung der Zieltechnologie

- O Drei Minimierungsansätze

- ⇒ algebraische Verfahren

- **⇒** graphische Verfahren

- Man unterscheidet

- ⇒ exakte Minimierungsverfahren (z.B. Quine McCluskey), deren Ergebnis das absolute Minimum einer Schaltungsdarstellung ist

- ⇒ heuristische Minimierungsverfahren auf der Basis von iterativen Minimierungsschritten

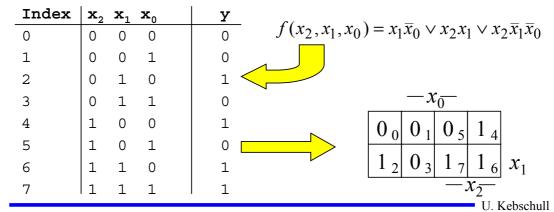

# Darstellung Boolescher Funktionen durch Funktionstabellen

- O Darstellung des Verhaltens einer Booleschen Funktion mit Hilfe einer vollständigen Funktionstabelle

- ⇒ Jeder Belegung der Booleschen Variablen wird ein Funktionswert zugeordnet

- $\Rightarrow f(x_2, x_1, x_0) \rightarrow y, mit \ x_i, y \in \{0,1\}$

| Index | $\mathbf{x}_{2}$ | $\mathbf{x}_{_{1}}$ | $\mathbf{x}_{0}$ | Y |

|-------|------------------|---------------------|------------------|---|

| 0     | 0                | 0                   | 0                | 0 |

| 1     | 0                | 0                   | 1                | 0 |

| 2     | 0                | 1                   | 0                | 1 |

| 3     | 0                | 1                   | 1                | 0 |

| 4     | 1                | 0                   | 0                | 1 |

| 5     | 1                | 0                   | 1                | 0 |

| 6     | 1                | 1                   | 0                | 1 |

| 7     | 1                | 1                   | 1                | 1 |

$$f(x_2, x_1, x_0) = x_1 \overline{x}_0 \lor x_2 x_1 \lor x_2 \overline{x}_1 \overline{x}_0$$

Technische Informatik 2 Stand SS 01 15

U. Kebschull

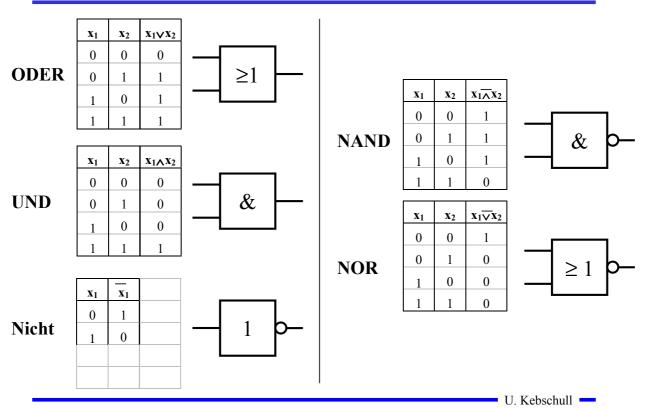

# Darstellung einiger zweistelliger Funktionen

Technische Informatik 2 Stand SS 01 16

#### Zusammenfassung der wichtigsten Begriffe aus TI1

O Boolesche Variable Variable, die den Wert wahr (1) oder falsch

(0) annehmen kann

O Produktterm: UND-Verknüpfung von Booleschen

Variablen

O Implikant: Produktterm, der eine oder mehrere "1"-

Stellen einer booleschen Funktion beschreibt

(impliziert)

O Implikat: Disjunktion (ODER-Verknüpfung) von

Literalen

O Minterm: Implikant, der genau eine "1"-Stelle einer

**booleschen Funktion beschreibt**

O Maxterm: Implikat, des genau eine "0"-Stelle einer

booleschen Funktion beschreibt

O disjunktive Normalform: Darstellung der Funktion, die nur aus

Mintermen besteht (DNF)

O konjunktive Normalform: Darstellung der Funktion, die nur aus

Maxtermen besteht (KNF)

Technische Informatik 2 Stand SS 01 U. Kebschull 17

#### **Beispiel**

Implikant

$$x_2 \wedge x_0 < x_2 \wedge x_1 \wedge x_0$$

$$x_2 \wedge \overline{x_1} \wedge x_0$$

**ONF**

$$f(x_2, x_1, x_0) = x_2 x_1 x_0 \lor x_2 \overline{x_1} x_0 \lor \overline{x_2} x_1 \overline{x_0} \lor \overline{x_2} \overline{x_1} \overline{x_0}$$

**Boolesche Variable**

• KNF

$$f(x_2, x_1, x_0) = (x_2 \lor x_1 \lor x_0) \land (x_2 \lor x_1 \lor \overline{x}_0) \land (x_2 \lor \overline{x}_1 \lor \overline{x}_0)$$

Implikat

$$x_2 \lor x_0 < x_1 \lor x_0 < x_2 \lor \overline{x_1} \lor x_0$$

# 1.1 KV-Diagramme

- O Nach Karnaugh und Veitch

- O Möglichkeit, Boolesche Funktionen übersichtlich darzustellen

- ⇒ bis 6 Variablen praktisch einsetzbar

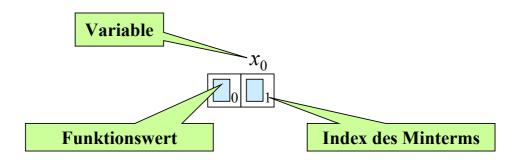

- O Ausgangspunkt ist ein Rechteck mit 2 Feldern

Technische Informatik 2 Stand SS 01 U. Kebschull 19

#### **KV-Diagramme**

#### Beispiele

$$\begin{bmatrix} x_0 \\ 0_0 & 1_1 \end{bmatrix}$$

$$f(x_0) = x_0$$

$$\begin{bmatrix} x_0 \\ 1_0 \end{bmatrix} \begin{bmatrix} 0_1 \end{bmatrix}$$

$$f(x_0) = \overline{x}_0$$

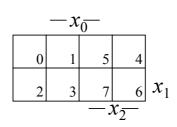

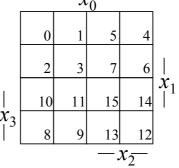

- **O** Erweiterung durch Spiegelung

- ⇒ für jede zusätzliche Variable verdoppelt sich die Zahl der Felder x<sub>0</sub>—

|   | $x_0$ |       |

|---|-------|-------|

| 0 | 1     |       |

| 2 | 3     | $x_1$ |

#### Eigenschaften von KV-Diagrammen

- **O** Jedes Feld ist ein Funktionswert

- ⇒ Ein Minterm der Funktion

- ⇒ Eindeutige Variablenzuordnung

- Oft werden  $x_1$  und  $x_2$  vertauscht

- **⇒** Lediglich eine andere Numerierung der Felder

- ⇒ Kein Einfluss auf das Minimierungsverfahren

- O Aufstellen der KV-Diagramme über die Funktionstabelle:

Technische Informatik 2 Stand SS 01 21

#### KV-Diagramme über die KNF

- O Argumentation über die Nullstellen der Funktion

- **⇒** Jede Nullstelle entspricht einem Maxterm

- O Beispiel

$$f(x_2, x_1, x_0) = x_1 \overline{x}_0 \lor x_2 x_1 \lor x_2 \overline{x}_1 \overline{x}_0$$

$$f(x_2, x_1, x_0) = (x_2 \lor x_1 \lor x_0) \land (x_2 \lor x_1 \lor \overline{x}_0) \land (x_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (\overline{x}_2 \lor x_1 \lor \overline{x}_0)$$

#### Minimalformen aus KV-Diagrammen

- O Zusammenfassen von Mintermen zu Implikanten

- O Beispiel:

23

Technische Informatik 2

Stand SS 01

# Implikant k-ter Ordnung

Def. 1.1: Es sei eine Boolesche Funktion  $f(x_0,...,x_{n-l}):B^n\to B$  gegeben. Ein Implikant k-ter Ordnung umfaßt  $2^k$  Felder eines KV-Diagramms.

- O Man erhält

- **⇒ Implikanten 0-ter Ordnung Minterme**

- □ Implikanten 1-ter Ordnung Zusammenfassung zweier Minterme

- ⇒ Implikanten 2-ter Ordnung

Zusammenfassung zweier

Implikanten 1-ter

Ordnung

⇒ usw.

#### Finden möglicher Zusammenfassungen

- O Finden von 1-Blöcken, die symmetrisch zu denjenigen Achsen, an denen eine Variable von 0 auf 1 wechselt

- Jede Funktion läßt sich als disjunktive Verknüpfung solcher Implikanten darstellen

- O Beispiele

U. Kebschull

Technische Informatik 2

Stand SS 01

25

#### Primimplikant

Def. 1.2: Es sei eine Boolesche Funktion  $f(x_0,...,x_{n-1}):B^n \to B$  gegeben. Ein Implikant p heißt Primimplikant, wenn es keinen Implikanten q gibt, der p impliziert.

- O Ein Primimplikant p ist von größtmöglicher Ordnung

- ⇒ Primimplikanten sind einfach aus einem KV-Diagramm herauszulesen

- ⇒ man sucht die größtmöglichen Implikanten

$$f(x_2, x_1, x_0) = x_2 x_1 \overline{x}_0 \lor x_2 x_0 \lor \overline{x}_2 \overline{x}_1 x_0$$

Primimplikanten

# Überdeckung

# Satz 1.1: Zu jeder Booleschen Funktion f gibt es eine minimale Überdeckung aus Primimplikanten

#### Bew. (Skizze):

Angenommen wir haben eine minimale Überdeckung der Funktion, die einen Implikanten k besitzt, der kein Primimplikant ist.

- ⇒ Dieser Implikant k kann durch einen Primimplikant p ersetzt werden, der k enthält

- ⇒ Das Ergebnis ist eine Überdeckung der Funktion f aus Primimplikanten mit der gleichen Anzahl von Termen

- ⇒ Die Überdeckung ist minimal

- O Einschränkung des Suchraums

- ⇒ man braucht nur die Primimplikanten für die Minimierung betrachten

U. Kebschull

Technische Informatik 2

Stand SS 01

27

#### Kernprimimplikant

Def. 1.3: Es sei eine Boolesche Funktion  $f(x_0,...,x_{n-1}):B^n \to B$  gegeben. Ein Implikant p heißt Kernprimimplikant, wenn er einen Minterm überdeckt, der von keinem anderen Primimplikant überdeckt wird.

- O Man nennt solche Primimplikanten auch <u>essentielle</u> Primimplikanten

- ⇒ Ein Kernprimimplikant muss auf jeden Fall in der disjunktiven Minimalform vorkommen

- O Ziel der Minimierung:

- Zwei Schritte

- 1. Finde alle Primimplikanten

- 2. Suche eine Überdeckung der Funktion mit möglichst wenigen Primimplikanten

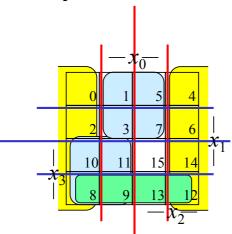

#### **Beispiel**

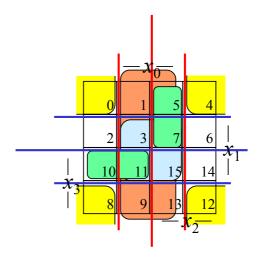

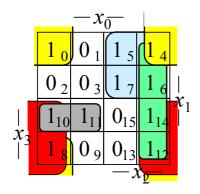

$$f(x_{3}, x_{2}, x_{1}, x_{0}) = \overline{x}_{3}\overline{x}_{2}\overline{x}_{1}\overline{x}_{0} \vee \overline{x}_{3}x_{2}\overline{x}_{1}\overline{x}_{0} \vee \overline{x}_{3}x_{2}\overline{x}_{1}x_{0} \vee

\overline{x}_{3}x_{2}x_{1}\overline{x}_{0} \vee \overline{x}_{3}x_{2}x_{1}x_{0} \vee x_{3}\overline{x}_{2}\overline{x}_{1}\overline{x}_{0} \vee

x_{3}\overline{x}_{2}x_{1}\overline{x}_{0} \vee x_{3}\overline{x}_{2}x_{1}x_{0} \vee x_{3}x_{2}\overline{x}_{1}\overline{x}_{0} \vee x_{3}x_{2}x_{1}\overline{x}_{0}

= MINt(0, 4, 5, 6, 7, 8, 10, 11, 12, 14)$$

$$e \overline{x_1}\overline{x_0}$$

(0,4,8,12)

$e \overline{x_3}x_2$  (4,5,6,7)

$x_2\overline{x_0}$  (4,6,12,14)

$x_3\overline{x_0}$  (8,10,12,14)

$e \overline{x_3}\overline{x_2}x_1$  (10,11)

$$f(x_3, x_2, x_1, x_0) = \overline{x}_1 \overline{x}_0 \vee \overline{x}_3 x_2 \vee x_3 \overline{x}_0 \vee x_3 \overline{x}_2 x_1$$

$$= \overline{x}_1 \overline{x}_0 \vee \overline{x}_3 x_2 \vee x_2 \overline{x}_0 \vee x_3 \overline{x}_2 x_1$$

**DMF**

U. Kebschull

Technische Informatik 2 Stand SS 01 29

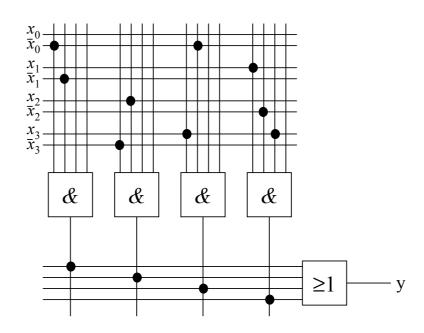

# Realisierung als "Programmable Logic Array (PLA)

$f(x_3, x_2, x_1, x_0) = \overline{x}_1 \overline{x}_0 \vee \overline{x}_3 x_2 \vee x_3 \overline{x}_0 \vee x_3 \overline{x}_2 x_1$

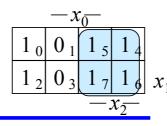

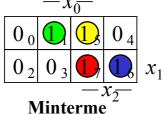

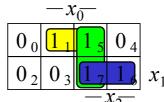

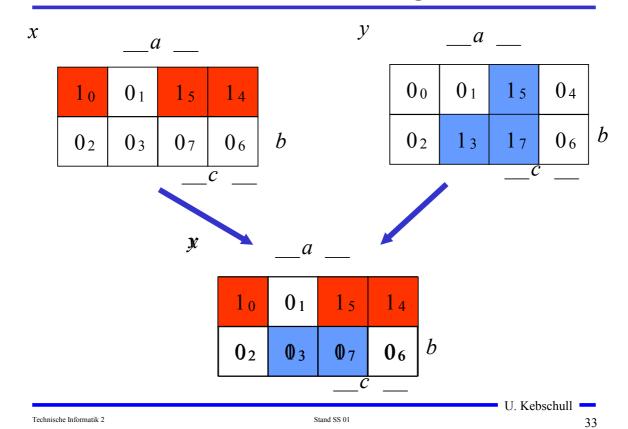

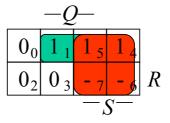

#### 1.2 Bündelminimierung

- O Funktionen mit mehreren Ausgängen werden gemeinsam minimiert

- **O** gemeinsame Implikanten sollten mehrfach genutzt werden

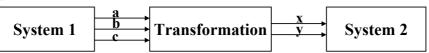

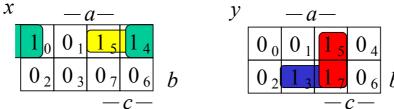

- **O** Beispiel: Transformation eines Codes

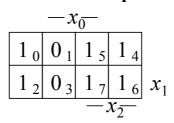

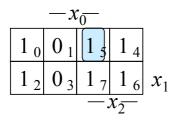

**O** Transformationstabelle

| System1 | System2 | $x: -x_{\overline{0}}$                                 |

|---------|---------|--------------------------------------------------------|

| c b a   | ху      | 1.0.1.1.                                               |

| 0 0 0   | 1 0     | 10011514                                               |

| 0 0 1   | 0 0     | $  0_2   0_3   0_7   0_6   x_1$                        |

| 0 1 1   | 0 1     | $-x_{\overline{2}}$                                    |

| 0 1 0   | 0 0     | y: -x <sub>0</sub> -                                   |

| 1 0 0   | 1 0     |                                                        |

| 1 0 1   | 1 1     | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| 1 1 0   | 0 0     | $  0_2   1_3   1_7   0_6   x_1$                        |

| 1 1 1   | 0 1     | $\frac{ z  +  z }{-x_2}$                               |

|         |         | U. Kebschull                                           |

Technische Informatik 2 Stand SS 01 31

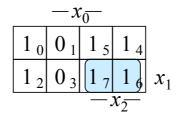

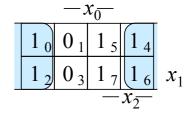

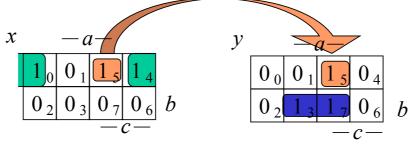

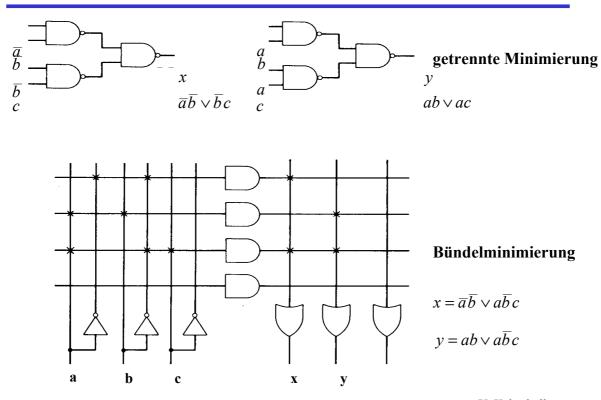

# Bündelminimierung

- **O** Getrennte Minimierung

- ⇒ insgesamt 4 Implikanten für die Realisierung

- Bündelminimierung

- ⇒ insgesamt 3 Implikanten für die Realisierung

# Bündelminimierung

# Bündelminimierung

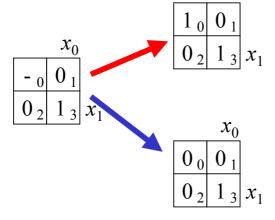

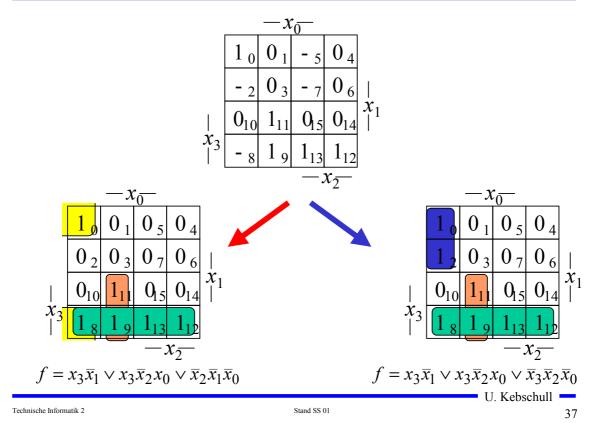

# 1.3 Unvollständig definierte Funktionen

- O Bisher war für alle Belegungen der Eingänge ein Funktionswert festgelegt

- ⇒ in praktischen Fällen kommt es sehr häufig vor, dass die Funktionswerte für bestimmte Eingangsbelegungen frei wählbar sind

- ⇒ diese Funktionswerte sind frei verfügbar

- O Solche Funktionen heißen <u>unvollständig</u> oder <u>partiell definierte</u> Funktionen

- ⇒ die nicht verwendeten Eingangsbelegungen heißen auch Don't-care-Belegungen

- ⇒ in KV-Diagrammen werden diese Felder mit einem "-" gekennzeichnet

- wichtiges Potential für die Minimierung!

- ⇒ um eine DMF zu erhalten, müssen diese mit "0" oder "1" belegt werden

U. Kebschull —

Technische Informatik 2

Stand SS 01

35

#### Minimierung unvollständiger Boolescher Funktionen

$$f(x_1, x_0) = x_1 x_0$$

#### Minimierung unvollständiger Boolescher Funktionen

#### 1.4 Das Verfahren nach Quine-McCluskey

- KV-Diagramme mit mehr als 6 Variablen werden sehr groß und unübersichtlich

- ⇒ dieses Problem wurde zuerst von Quine und McCluskey erkannt und gelöst

- ⇒ das Verfahren nach Quine-McCluskey ist ein tabellarisches Verfahren

- ⇒ es führt auf eine DMF (disjunktive minimale Form)

- O Ausgangspunkt ist die Funktionstabelle der Funktion

- nur die Minterme werden berücksichtigt

- O Der Suchraum wird eingeschränkt, weil der Satz 1.1 gilt:

- ⇒ zu jeder Booleschen Funktion f gibt es eine minimale Überdeckung aus Primimplikanten

- O Verfahren nach Quine McCluskey in 2 Schritten:

- 1. Schritt: berechne alle Primimplikanten

- 2. Schritt: suche eine minimale Überdeckung aller Minterme

#### Beispiel: Die vollständige Funktionstabelle

| Nr. | edcba     | У | Nr. | edcba     | У |

|-----|-----------|---|-----|-----------|---|

| 0   | 0 0 0 0 0 | 0 | 16  | 1 0 0 0 0 | 0 |

| 1   | 0 0 0 0 1 | 0 | 17  | 10001     | 0 |

| 2   | 0 0 0 1 0 | 1 | 18  | 10010     | 1 |

| 3   | 0 0 0 1 1 | 0 | 19  | 10011     | 0 |

| 4   | 0 0 1 0 0 | 1 | 20  | 10100     | 0 |

| 5   | 0 0 1 0 1 | 1 | 21  | 10101     | 0 |

| 6   | 0 0 1 1 0 | 1 | 22  | 10110     | 1 |

| 7   | 0 0 1 1 1 | 0 | 23  | 10111     | 0 |

| 8   | 0 1 0 0 0 | 0 | 24  | 1 1 0 0 0 | 0 |

| 9   | 0 1 0 0 1 | 0 | 25  | 1 1 0 0 1 | 0 |

| 10  | 0 1 0 1 0 | 1 | 26  | 1 1 0 1 0 | 1 |

| 11  | 0 1 0 1 1 | 0 | 27  | 1 1 0 1 1 | 0 |

| 12  | 0 1 1 0 0 | 1 | 28  | 1 1 1 0 0 | 0 |

| 13  | 0 1 1 0 1 | 1 | 29  | 1 1 1 0 1 | 0 |

| 14  | 0 1 1 1 0 | 1 | 30  | 11110     | 1 |

| 15  | 0 1 1 1 1 | 0 | 31  | 11111     | 0 |

Technische Informatik 2 Stand SS 01 U. Kebschull 39

#### 1. Schritt: Berechnung aller Primimplikanten

- Schreibweise

- **⇒ 1** steht für eine nicht negierte Variable

- ⇒ 0 steht für eine negierte Variable

- ⇒ steht für eine nicht auftretende Variable

- **O** Man betrachtet nur die Minterme

- ⇒ 1-Stellen der Funktion

- O Die Minterme werden geordnet

- Gruppen mit der gleichen Anzahl von Einsen

- innerhalb der Gruppen: aufsteigende Reihenfolge

- ⇒ man erhält die 1. Quinesche Tabelle, 0. Ordnung

- O Minterme benachbarter Gruppen die sich nur in 1 Variable unterscheiden werden gesucht

- ⇒ diese können durch Streichen der Variable zusammengefaßt werden

- ⇒ man erhält die 1. Quineschen Tabellen höherer Ordnung

#### Beispiel: 1. Quinesche Tabelle

| Nr. | edcba     | Nr. edcba       | Nr. edcba               |

|-----|-----------|-----------------|-------------------------|

| 2   | 0 0 0 1 0 | 2,6 00-10       | 2,6,10,14 0 1 0         |

| 4   | 0 0 1 0 0 | 2,10 0 - 0 1 0  | 2,6,18,22 - 0 - 1 0     |

| 5   | 0 0 1 0 1 | 2,18 - 0 0 1 0  | 2,10,18,26 0 1 0        |

| 6   | 0 0 1 1 0 | 4,5 0010-       | 4,5,12,13 0 - 1 0 - $A$ |

| 10  | 0 1 0 1 0 | 4,6 001-0       | 4,6,12,14               |

| 12  | 0 1 1 0 0 | 4,12 0 - 1 0 0  | 6,14,22,30 1 1 0        |

| 18  | 1 0 0 1 0 | 5,13 0 - 1 0 1  | 10,14,26,30 - 1 - 1 0   |

| 13  | 0 1 1 0 1 | 6,14 0 - 1 1 0  | 18,22,26,30 1 1 0       |

| 14  | 0 1 1 1 0 | 6,22 - 0 1 1 0  | 2. Ordnung              |

| 22  | 1 0 1 1 0 | 10,14 0 1 - 1 0 | 2. Ordining             |

| 26  | 1 1 0 1 0 | 10,26 - 1 0 1 0 |                         |

| 30  | 1 1 1 1 0 | 12,13 0 1 1 0 - |                         |

| 0   | OI        | 12,14 0 1 1 - 0 |                         |

| U.  | Ordnung   | 18,22 1 0 - 1 0 | Nr. edcba               |

|     |           | 18,26 1 - 0 1 0 | 2,6,10,14               |

|     |           | 14,30 - 1 1 1 0 | 18,22,26,30 1 0         |

|     |           | 22,30 1 - 1 1 0 | 3. Ordnung              |

|     |           | 26,30 1 1 - 1 0 |                         |

|     |           | 1. Ordnung      |                         |

|     |           | 8               | U. Kebschull            |

Stand SS 01

41

U. Kebschull

# 2. Schritt: Suche einer minimalen Überdeckung

O Aufstellen der 2. Quineschen Tabelle

Technische Informatik 2

- ⇒ alle Primimplikanten werden zusammen mit der Nummer des Minterms aus dem sie hervorgegangen sind in eine Überdeckungstabelle eingetragen

- O Kosten für einen Primimplikanten:

- ⇒ Anzahl der UND-Eingänge (Anzahl der Variablen des Terms)

| Primimplikant | 2 | 4 | 5 | 6 | 10 | 12 | 13 | 14 | 18 | 22 | 26 | 30 | Kosten |

|---------------|---|---|---|---|----|----|----|----|----|----|----|----|--------|

| A             |   | x | X |   |    | x  | x  |    |    |    |    |    | 3      |

| В             |   | X |   | X |    | X  |    | X  |    |    |    |    | 3      |

| С             | х |   |   | х | X  |    |    | x  | X  | x  | X  | X  | 2      |

O Aufgabe: Finden einer Überdeckung aller Minterme mit minimalen Kosten

#### Systematische Lösung des Überdeckungsproblems

- $oldsymbol{\circ}$  Aufstellung einer Überdeckungsfunktion  $\ddot{u}_f$

- $\Rightarrow w_A, w_B$  und  $w_C$  sind Variablen, die kennzeichnen, ob ein entsprechender Primimplikant in der vereinfachten Darstellung aufgenommen wird, oder nicht

$= w_C w_B w_A \vee w_A w_C$

$(= w_A w_C)$

U. Kebschull

Technische Informatik 2

Stand SS 01

43

# Systematische Lösung des Überdeckungsproblems

- **O** Ergebnis nach der Vereinfachung:  $\ddot{u}_f = w_C w_B w_A \vee w_A w_C$

- O Damit f ganz überdeckt ist, muss  $\ddot{u}_f$  eine Tautologie sein

- ⇒ man sucht einen konjunktiven Term mit minimalen Kosten

$$w_C w_B w_A$$

**Kosten:**  $3 + 3 + 2 = 8$

$$w_A w_C$$

Kosten: 3 + 2 = 5

$\bigcirc$  Als Endergebnis der Minimierung für die Funktion f erhält man

$$f(e,d,c,b,a) = \overline{e}c\overline{b} \vee b\overline{a}$$

# Vereinfachung des Überdeckungsproblems

- O Die Primimplikantentabelle kann reduziert werden, indem essentielle Primterme (Kernprimimplikanten) und die von ihnen überdeckten Minterme gestrichen werden

- ⇒ tragen mit einem einzigen "X" zu einer Spalte bei

- ⇒ müssen auf jeden Fall in der Überdeckung enthalten sein

- O In diesem Beispiel sind dies die beiden Primimplikanten A und C

- ⇒ A: 5, 13

- ⇒ C: 2, 10, 18, 22, 26, 30

- ⇒ B ist vollständig überdeckt und kann ebenfalls gestrichen werden

Technische Informatik 2 Stand SS 01 U. Kebschull 45

#### Aufwandsbetrachtungen

- O Alle Verfahren benötigen 2 Schritte

- ⇒ 1. Erzeugen aller Primimplikanten (Primimplikate)

- ⇒ 2. Auswahl der Primiplikanten (Primimplikate), welche die Minterme (Maxterme) mit minimalen Kosten überdecken

- O Die Anzahl der Primimplikanten (Primimplikaten) kann exponentiell steigen

$\Rightarrow \text{ Es gibt Funktionen mit } \frac{3^n}{n} \text{ Primimplikanten}$

- O Das Überdeckungsproblem ist NP-Vollständig

- ⇒ es besteht wenig Hoffnung einen Algorithmus zu finden, der dieses Problem polynomial mit der Zahl der Eingabevariablen löst

#### Heuristische Verfahren

- O Heuristische Minimierungsverfahren werden eingesetzt,

- wenn die zweistufige Darstellung optimiert werden muss, aber

- ⇒ nur begrenzte Rechenzeit und Speicherplatz zur Verfügung steht

- O Die meisten heuristischen Minimierungsansätze basieren auf einer schrittweisen Verbesserung der Schaltung

- **O** Unterschiede zu exakten Verfahren:

- ⇒ man wendet eine Menge von Transformationen direkt auf die Überdeckung des *ON-Sets* an

- ⇒ man definiert die Optimierung als beendet, wenn diese Transformationen keine Verbesserungen mehr bringen

U. Kebschull

Technische Informatik 2

Stand SS 01

#### 1.5 Laufzeiteffekte in Schaltnetzen

- O Bisher wurden Schaltnetze mit idealen Verknüpfungsgliedern betrachtet

- ⇒ die Verknüpfungsgliedern besaßen keine Signallaufzeit

- O Bei realen Verknüpfungsgliedern dürfen Signallaufzeiten nicht vernachlässigt werden

- ⇒ Schaltvariablen können Werte annehmen, die theoretisch oder bei idealen Verknüpfungsgliedern nie auftreten könnten

- O Solche Störimpulse nennt man Hazards

- ⇒ sie treten als Antwort auf die Änderung der Werte der Eingangsvariablen auf

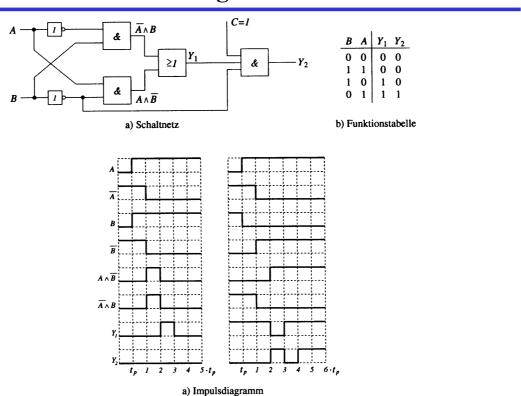

#### **Entstehung von Hazards**

Technische Informatik 2 Stand SS 01

#### **Statische Hazards**

O Statische Hazards sind Störimpulse aus einer Verknüpfung, die theoretisch konstant Null oder Eins liefern müsste

$X_t \wedge \overline{X}_{t-k}$  müsste Null liefern statischer 1-Hazard bei einem Übergang von X: 0 $\to$ 1

$X_t \vee \overline{X}_{t-k}$  müsste Eins liefern statischer 0-Hazard bei einem Übergang von X: 1 $\to$ 0

#### **Dynamische Hazards**

- O Dynamische Hazards entstehen als zusätzliche Übergänge beim Ausgang eines Schaltnetzes

- $X_t \wedge \overline{X}_{t-k} \vee X_l$ , mit l > k

- $\Rightarrow$  bei einem Übergang von X=0  $\rightarrow X=1$  darf am Ausgang nur ein zu  $X_{t-1}$  synchroner  $0 \rightarrow 1$  Übergang auftreten

- $\Rightarrow$  durch den vorgeschalteten statischen Hazard kommt es aber zu einer zusätzlichen  $0 \rightarrow 1$  Flanke

- $X_t \wedge (\overline{X}_{t-k} \vee X_l)$ , mit l > k

- $\Rightarrow$  bei einem Übergang von X=0  $\to X=1$  darf am Ausgang nur ein zu  $X_t$  synchroner 0  $\to 1$  Übergang auftreten

- $\Rightarrow$  durch den vorgeschalteten statischen Hazard kommt es aber zu einer zusätzlichen  $0 \rightarrow 1$  Flanke

Technische Informatik 2 Stand SS 01 U. Kebschull

#### Klassifikation von Hazards

#### **Behebung von Hazards**

- O Hazards können die Funktion von Schaltnetzen stören

- ⇒ falsche Werte können an den Eingang eines Schaltnetzes zurückgekoppelt werden

- O Um solche Fehler zu vermeiden werden taktflankengetriggerte Speicherglieder in die Rückkopplung eingefügt

- O Die Signale werden erst übernommen, wenn die Hazards abgeklungen sind

- nur stabile, gültige Werte werden übernommen

- ⇒ synchrone Schaltwerke: Schaltwerke, die durch einen zentralen Takt gesteuert werden

- O Hazards haben einen Einfluss auf die maximale Schaltgeschwindigkeit

- maximaler Takt

- ⇒ Entfernung von Hazards führt zu einer Erhöhung der Geschwindigkeit einer Schaltung

Technische Informatik 2 Stand SS 01 U. Kebschull 53

# 2 Speicherglieder

- O Speicherglieder dienen der Aufnahme, Speicherung und Abgabe von Schaltvariablen

- ⇒ Ein Speicherglied ist ein bistabiles Kippglied

- **⇒** Flipflop

- Zwei Zustände

- ⇒ Zustand 1: Setzzustand

- ⇒ Zustand 0: Rücksetzzustand

- O Übernahme des Zustands kann erfolgen

- ⇒ taktunabhängig (nicht taktgesteuert)

- ⇒ taktabhängig (taktgesteuert)

- taktzustandsgesteuert

- taktflankengesteuert

- O Die unterschiedlichen Arten der Ansteuerungen führen zu unterschiedlichen Flipflop-Typen

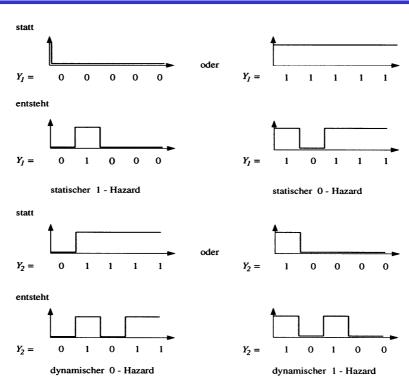

#### **Funktionsprinzip**

- Rückkopplung

- **⇒** Wirkprinzip aller bistabilen Kippschaltungen

- $\Rightarrow$  Ein Kippvorgang eines stabilen Zustands in den anderen wird durch  $E_{st1}$  und  $E_{st2}$  ausgelöst

Technische Informatik 2 Stand SS 01 U. Kebschull 55

#### **Funktionsprinzip**

- $\bigcirc$  Nach dem Anlegen von  $U_B$  sei  $T_2$  leitend,  $T_I$  sperrt

- $\Rightarrow$   $A_1$  besitzt H-Pegel und  $A_2$  besitzt L-Pegel

- **⇒** dieser Zustand ist stabil

- $\bigcirc$  Wird  $E_{stl}$  auf H-Pegel gesetzt, so

- $\Rightarrow$  wird  $T_I$  leitend,  $A_I$  geht auf L-Pegel

- $\Rightarrow$   $T_2$  sperrt und  $A_2$  geht auf H-Pegel

- **⇒** dieser Zustand ist ebenfalls stabil

- $\bigcirc$  Wird  $E_{st2}$  auf H-Pegel gesetzt, so

- $\Rightarrow$  wird  $T_2$  leitend,  $A_2$  geht auf L-Pegel

- $\Rightarrow T_I$  sperrt und  $A_I$  geht auf H-Pegel

- **⇒** dieser Zustand ist wiederum stabil

- $\bigcirc$  Werden  $E_{st1}$  und  $E_{st2}$  auf H-Pegel gesetzt, so

- ⇒ leiten beide Transistoren, die Rückkopplung wird unwirksam

- ⇒ dieser Zustand ist nicht stabil

- unzulässige Eingangsbelegung

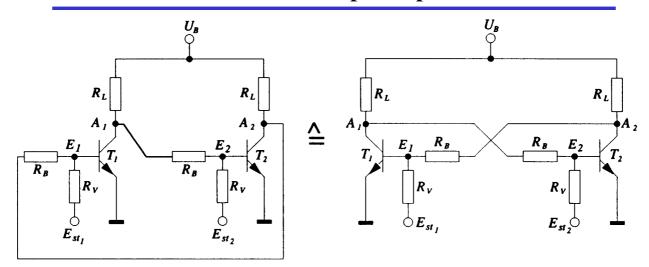

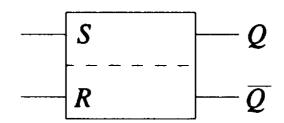

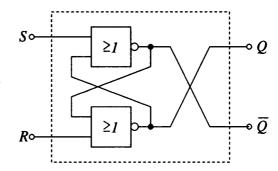

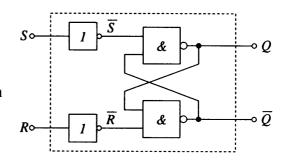

#### **RS-Flipflop**

- O Bistabile Kippschaltungen können aus rückgekoppelten

- **⇒** Transistoren

- **⇒** NOR-Gattern

- **⇒** NAND-Gattern

gebaut werden

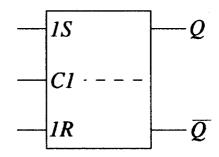

- O RS-Flipflop

- ⇒ wenn die Eingänge den Wert 0 haben, bleibt der vorherige Zustand stabil

- $\Rightarrow$  wird S =1, wird Q=1 und  $\overline{Q}$ =0

- $\Rightarrow$  wird R=1, wird Q=0 und  $\overline{Q}$ =1

- ⇒ S=1 und gleichzeitig R=1 sind nicht zulässig

Schaltzeichen für ein RS-Flipflop nach DIN

Technische Informatik 2 Stand SS 01 U. Kebschull 57

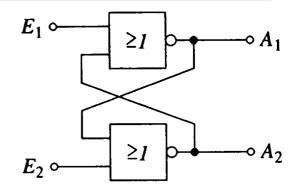

# RS-Flipflop aus NOR-Gattern

- O Liegt an einem Eingang eines NOR-Gatters eine 1 an, so geht der entsprechende Ausgang auf 0

- Liegen an beiden Eingängen eine 0 an, so bleiben die Ausgänge erhalten

Funktionstabelle der Ausgänge A<sub>1</sub> und A<sub>2</sub>

| $\boldsymbol{E}_1$ | $\boldsymbol{E_2}$ | $A_1$ | $A_2$             |

|--------------------|--------------------|-------|-------------------|

| 0                  | 0                  | (wie  | vorher) speichern |

| 0                  | 1                  | 1     | 0                 |

| 1                  | 0                  | 0     | 1                 |

| 1                  | 1                  | (0    | 0) unzulässig     |

#### RS-Flipflop aus NOR-Gattern

O Ein RS-Flipflop entsteht durch Vertauschen der Ausgänge

#### **Funktionstabelle**

| $\mathbf{S}$ | R | Q    | $\overline{\mathbf{Q}}$ |

|--------------|---|------|-------------------------|

| 0            | 0 | (wie | vorher) speichern       |

| 0            | 1 | 0    | 1                       |

| 1            | 0 | 1    | 0                       |

| 1            | 1 | ( 0  | 0) unzulässig           |

Technische Informatik 2 Stand SS 01 U. Kebschull 59

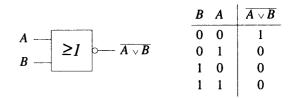

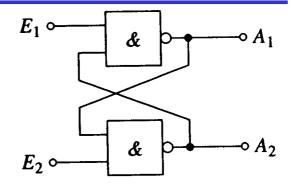

#### RS-Flipflop aus NAND-Gattern

- O Liegt an beiden Eingängen eines NAND-Gatters eine 1 an, so geht der entsprechende Ausgang auf 0

- O Liegen an beiden Eingängen der Schaltung eine 1 an, so bleiben die Ausgänge erhalten

#### Funktionstabelle der Ausgänge A<sub>1</sub> und A<sub>2</sub>

| $E_1$ | $\boldsymbol{E_2}$ | $A_1$ $A_2$                                                                     |   |   |                         |

|-------|--------------------|---------------------------------------------------------------------------------|---|---|-------------------------|

| 0     | 0                  | (1 1) (unzulässig)                                                              | В | A | $\overline{A \wedge R}$ |

| 0     | 1                  | 1 0                                                                             | - |   | 1                       |

| 1     | 0                  | $0 \qquad 1 \qquad \stackrel{A}{\longrightarrow} \& \sim \overline{A \wedge B}$ | 0 | 1 | 1                       |

| 1     | 1                  | (wie vorher) speichern                                                          | 1 | 0 | 1                       |

| -     | -                  | ( vor) «pore»                                                                   | 1 | 1 | 0                       |

U. Kebschull —

Technische Informatik 2 Stand SS 01 60

#### RS-Flipflop aus NAND-Gattern

**OEin RS-Flipflop entsteht durch Negation der Eingänge**

#### **Funktionstabelle**

| S | R | $\overline{\mathbf{S}}$ | $\overline{\mathbf{R}}$ | Q    | $\overline{\mathbf{Q}}$ |

|---|---|-------------------------|-------------------------|------|-------------------------|

| 0 | 0 | 1                       | 1                       | (wie | vorher) speichern       |

| 0 | 1 | 1                       | 0                       | 0    | 1                       |

| 1 | 0 | 0                       | 1                       | 1    | 0                       |

| 1 | 1 | 0                       | 0                       | (1   | 1) unzulässig           |

Technische Informatik 2 Stand SS 01 U. Kebschull 61

#### Zustandsfolgetabelle

- O Das Ausgangssignal ändert sich zeitversetzt nach der Signaländerung am Eingang

- Zeitverhalten wird in einer Zustandsfolge dargestellt

- $\Rightarrow Q_n$  ist der Wert vor der Signaländerung

- $\Rightarrow Q_{n+1}$  ist der Wert nach der Signaländerung

| S | R | $Q_n$ | $Q_{n+1}$ |            |

|---|---|-------|-----------|------------|

| 0 | 0 | 0     | 0         | speichern  |

| 0 | 0 | 1     | 1         | speichern  |

| 0 | 1 | 0     | 0         | rücksetzen |

| 0 | 1 | 1     | 0         | rücksetzen |

| 1 | 0 | 0     | 1         | setzen     |

| 1 | 0 | 1     | 1         | setzen     |

| 1 | 1 | 0     | -         | unzulässig |

| 1 | 1 | 1     | -         | unzulässig |

$$Q_{n+1} = S \vee (\overline{R} \wedge Q_n)$$

- O Diese Gleichung heißt auch Funktionsgleichung oder Übergangsfunktion eines RS-Flipflops

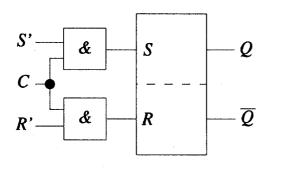

#### RS-Flipflop mit Zustandssteuerung

- O Beim RS-Flipflop wird der Ausgang sofort nach Anlegen der Eingangssignale gesetzt

- ⇒ zur Vermeidung von Hazards wird häufig gefordert, dass ein Flipflop seinen Wert nur zu bestimmten Zeitpunkten ändert

- **⇒** Synchrone Schaltwerke

- **⇒** Einführung eines Taktsignals

Schaltzeichen

U. Kebschull

Technische Informatik 2

Stand SS 01

63

# RS-Flipflop mit Zustandssteuerung

#### **Funktionstabelle**

| <u>C</u> | S | R | $Q_n$ | $Q_n$ | ±1             |

|----------|---|---|-------|-------|----------------|

| 0        | 0 | 0 | 0     | 0     | Ī              |

| 0        | 0 | 0 | 1     | 1     | keine Änderung |

| 0        | 0 | 1 | 0     | 0     | des            |

| 0        | 0 | 1 | 1     | 1     | Ausgangs-      |

| 0        | 1 | 0 | 0     | 0     | zustands       |

| 0        | 1 | 0 | 1     | 1     | d.h.           |

| 0        | 1 | 1 | 0     | 0     | Speichern      |

| 0        | 1 | 1 | 1     | 1     |                |

| 1        | 0 | 0 | 0     | 0     | speichern      |

| 1        | 0 | 0 | 1     | 1     | speichern      |

| 1        | 0 | 1 | 0     | 0     | rücksetzen     |

| 1        | 0 | 1 | 1     | 0     | rücksetzen     |

| 1        | 1 | 0 | 0     | 1     | setzen         |

| 1        | 1 | 0 | 1     | 1     | setzen         |

| 1        | 1 | 1 | 0     | _     | unzulässig     |

| 1        | 1 | 1 | 1     | -     | unzulässig     |

Aus der Übergangsfunktion des RS-Flipflos

$$Q_{n+1} = S \vee (\overline{R} \wedge Q_n)$$

mit  $S = (C \wedge S')$  und  $R = (C \wedge R')$

$$Q_{n+1} = (C \wedge S') \vee ((\overline{C \wedge R'}) \wedge Q_n)$$

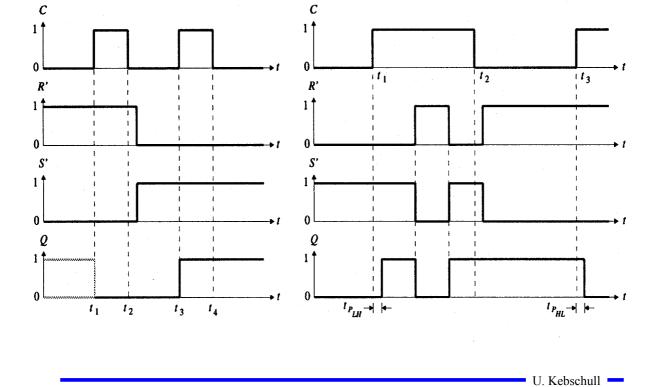

# Impulsdiagramm für Taktzustandssteuerung

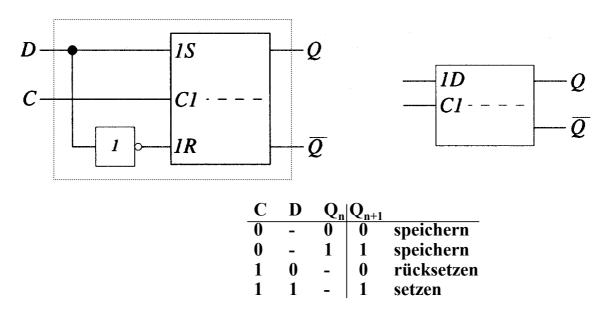

# **D-Flipflop mit Zustandssteuerung**

Stand SS 01

O Das D-Flipflop entsteht aus einem RS-Flipflop mit Zustandssteuerung, durch die Negation des Setzsignals S

U. Kebschull —

Technische Informatik 2

65

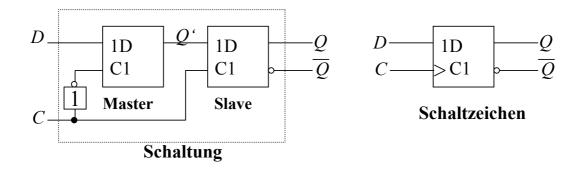

#### **Master-Slave D- Flipflop**

- O Probleme beim Verketten von Flipflops

- ⇒ bei C=1 rutschen die Eingänge bis zum Ausgang durch

- ⇒ Anwendung: Schieberegister, Zähler

- O Lösung: (positiv) flankengesteuertes Flipflop

- ⇒ zwei D-Flipflops werden hintereinander geschaltet

- ⇒ das erste Flipflop erhält den negierten Takt

- **⇒** Master-Slave-Prinzip

Technische Informatik 2 Stand SS 01 U. Kebschull 67

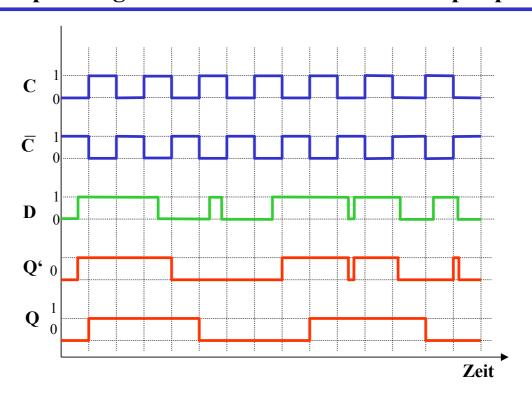

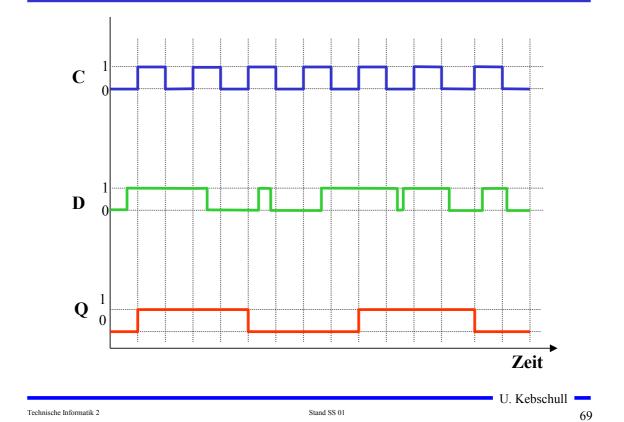

#### Impulsdiagramm des Master-Slave D-Flipflops

Technische Informatik 2 Stand SS 01

#### Impulsdiagramm des Master-Slave D-Flipflops

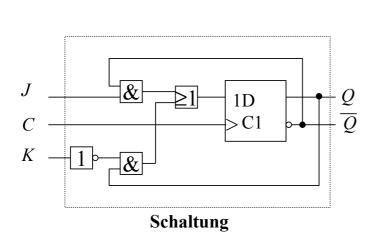

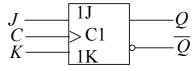

# JK-Flipflop

- O Neben den Funktionen <u>speichern</u>, <u>setzen</u> und <u>rücksetzen</u>, macht es Sinn für die undefinierte Belegung R=S=1 die weitere Funktion <u>wechseln</u> zu definieren

- ⇒ Man erreicht dies durch Rückführung der Ausgänge an den Eingang

#### Schaltzeichen

| J                       | K | $Q_{n+}$                             | 1          |

|-------------------------|---|--------------------------------------|------------|

| $\overline{0}$          | 0 | $Q_n$                                | speichern  |

| 0                       | 1 | 0                                    | rücksetzen |

| 1                       | 0 | 1                                    | setzen     |

| 1                       | 1 | $\overline{\mathbf{Q}}_{\mathbf{n}}$ | wechseln   |

| <b>Funktionstabelle</b> |   |                                      |            |

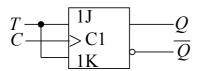

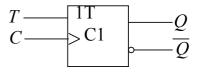

#### **Master-Slave T-Flipflop**

- O Ein T-Flipflop besitzt wie das D-Flipflop nur einen Eingang

- ist dieser gleich 1, wechselt das Flipflop seinen Wert

- **⇒** T steht für toggle

Schaltung

Schaltzeichen

#### 3 Schaltwerke

#### 3.1 Formale Grundlagen

- Schaltnetze

- ⇒ die Ausgabe einer Schaltung hängt nur von den Werten der Eingabe zum gleichen Zeitpunkt ab

- ⇒ man nennt sie auch kombinatorische Schaltungen

- Schaltwerke

- ⇒ die Ausgabe einer Schaltung kann von den Werten der Eingabe zu vergangenen Zeitpunkten abhängen

- ⇒ alle Abhängigkeiten von Werten der Vergangenheit werden in einem Zustand zusammengefaßt

- ⇒ sie sind Implementierungen von deterministischen endlichen Automaten

Technische Informatik 2 Stand SS 01 72

### Beschreibung von endlichen Automaten

- O Andere Namen für endliche Automaten sind:

- ⇒ finite state machine, FSM

- **⇒** sequentielle Schaltungen

- **⇒** Schaltungen mit Speicherverhalten

- **•** Aus der Automatentheorie:

Ein endlicher Automat ist ein Quintupel A=(X, Y, S,  $\delta$ ,  $\lambda$ ,  $s_0$ )

- $\Rightarrow$  eine endliche Menge von Eingangsbelegungen, X

- ⇒ eine endliche Menge von Ausgangsbelegungen, Y

- $\Rightarrow$  eine endliche Menge von Zuständen, S

- $\Rightarrow$  eine Zustandsübergangsfunktion  $\delta: X \times S \rightarrow S$

- **⇒** eine Ausgabefunktion

$\lambda: X \times S \to Y$  (Mealy Verhalten)

$\lambda: S \to Y$  (Moore Verhalten)

$\Rightarrow$  und er besitzt einen Startzustand  $s_0$

Technische Informatik 2 Stand SS 01

U. Kebschull

73

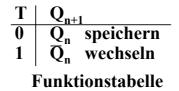

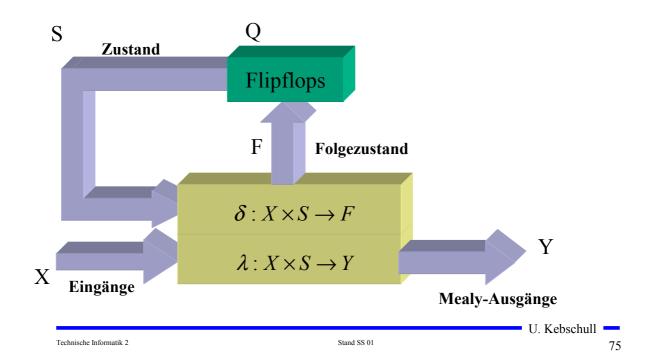

# Mealy- und Moore-Automaten

- O Die Zustände eines endlichen Automaten werden in Flipflops gespeichert

- ⇒ möglich sind D-, T-, JK-, RS-Flipflops

- O Der aktuelle Zustand wird an den Eingang der Schaltung rückgekoppelt

- **○** Man unterscheidet Mealy- und Moore- und Medvedev-Automaten:

- O Mealy:

- ⇒ Ausgangsleitungen können sich ändern, auch wenn keine Taktflanke aufgetreten ist

- Moore:

- ⇒ Änderung von Ausgangsleitungen nur mit Änderung eines Taktimpulses

- Medvedev:

- **⇒** Spezialfall des Moore-Automaten

- ⇒ die Ausgänge sind die Zustandsbits der Flipflops

# **Struktur eines Mealy-Automaten**

# **Struktur eines Moore-Automaten**

Technische Informatik 2 Stand SS 01 76

# 3.2 Darstellung endlicher Automaten

- O Die Aufgabenstellung liegt meist in einer nicht formalisierten Form vor

- O Um beim Entwurf von Schaltwerken systematische und möglichst auch rechnergestützte Entwurfsverfahren einsetzen zu können, muss eine formalisierte Beschreibung verwendet werden

- O Häufig verwendete Darstellungsformen sind:

- **⇒** Zeitdiagramm

- **⇒** Automatengraph

- **⇒** Ablauftabelle

- **⇒** Schaltfunktionen

- **⇒** Automatentabelle

U. Kebschull

Technische Informatik 2

Stand SS 01

# Beispiel: Selbsthalteschaltung

- O Beschreibung der Funktion:

- ⇒ an den Eingängen befinden sich zwei Tasten : (Start und Stopp)

- ⇒ die Schaltung liefert ein Ausgangssignal, mit dem ein Gerät einoder ausgeschaltet werden kann

- wird die Starttaste gedrückt, soll das Gerät eingeschaltet werden

- ⇒ es soll eingeschaltet bleiben, auch wenn die Starttaste wieder losgelassen wird

- ⇒ das Gerät soll ausgeschaltet werden, sobald die Stopptaste betätigt wird

- O zu klären ist:

- ⇒ was passiert, wenn beide Tasten gleichzeitig betätigt werden?

- ⇒ was passiert, wenn die Starttaste gedrückt wird, obwohl das Gerät eingeschaltet ist?

- ⇒ was passiert, wenn das Gerät ausgeschaltet ist und die Stopptaste gedrückt wird?

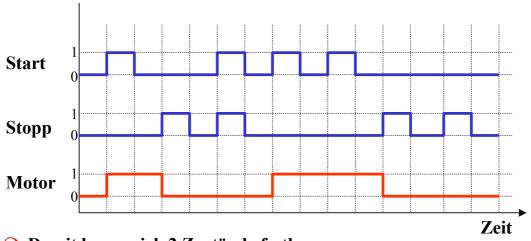

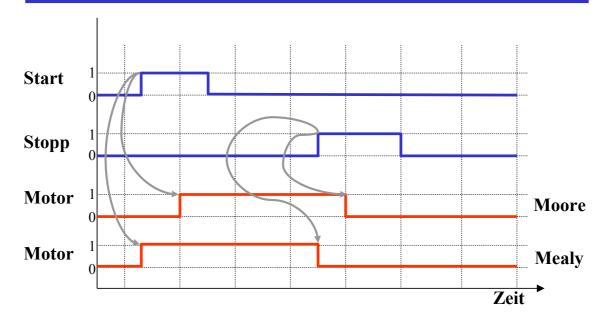

# Zeitdiagramm

- O Damit lassen sich 2 Zustände festlegen:

- $\Rightarrow$  **Zustand**  $s_0$ : **Ausgabe von** Motor=0 **und warten auf** Start=1 **und** Stopp=0

- $\Rightarrow$  **Zustand**  $s_1$ : **Ausgabe von** Motor=1 **und warten auf** Stopp=1

Technische Informatik 2 Stand SS 01 U. Kebschull 79

# Mealy und Moore Verhalten

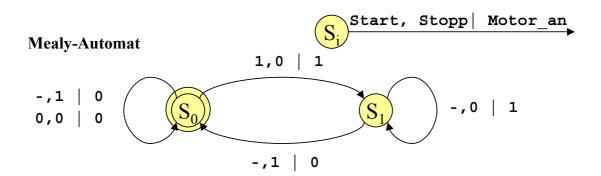

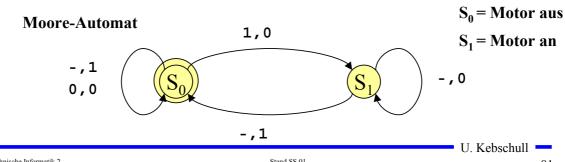

# Automatengraph

Technische Informatik 2 Stand SS 01 81

# Ablauftabelle

#### Mealy-Ablauftabelle

| Eingang | Zustand | Folgezustand | Ausgang |

|---------|---------|--------------|---------|

| -, 1    | S0      | S0           | 0       |

| 0, 0    | S0      | S0           | 0       |

| 1, 0    | S0      | S1           | 1       |

| -, 0    | S1      | S1           | 1       |

| -, 1    | S1      | S0           | 0       |

#### Moore-Ablauftabelle

Technische Informatik 2

| Eingang | Zustand / | Folgezustand |

|---------|-----------|--------------|

|         | Ausgang   |              |

| -, 1    | S0/ 0     | S0           |

| 0, 0    | S0/ 0     | S0           |

| 1, 0    | S0/ 0     | S1           |

| -, 0    | S1/ 1     | S1           |

| -, 1    | S1/ 1     | S0           |

Stand SS 01 82

# Interpretation der Ablauftabelle

Wenn wir im Zustand 0 sind

und zusätzlich Start = 1 und Stop = 0 gilt,

dann wird Motor\_an zu 1

und wir gehen mit dem nächsten Takt in den Zustand 1

Technische Informatik 2 Stand SS 01 U. Kebschull 83

# Schaltfunktionen

• Aus der Ablauftabelle lassen sich die die Ausgabe- und die Zustandsübergangsfunktion ablesen:

| $X_1, X_2$ | Zustand S | Folgezustand S <sup>+</sup> | Ausgang y |

|------------|-----------|-----------------------------|-----------|

| -, 1       | S0        | S0                          | 0         |

| 0, 0       | S0        | S0                          | 0         |

| 1, 0       | S0        | S1                          | 1         |

| -, 0       | S1        | S1                          | 1         |

| -, 1       | S1        | S0                          | 0         |

**O Übergangsfunktion:**  $s_0^+ = (x_2 \wedge s_0) \vee (\overline{x}_1 \wedge \overline{x}_2 \wedge s_0) \vee (x_2 \wedge s_1)$  $s_1^+ = (x_1 \wedge \overline{x}_2 \wedge s_0) \vee (\overline{x}_2 \wedge s_1)$

**Ausgabefunktion:**  $y = (x_1 \wedge \overline{x}_2 \wedge s_0) \vee (\overline{x}_2 \wedge s_1)$  **Mealy-Automat**  $y = s_1$  **Moore-Automat**

Technische Informatik 2 Stand SS 01

#### **Automatentabelle**

| Folgezustand |             |       |         |         | Folgezustand/ Ausgang |       |         |           |         |         |

|--------------|-------------|-------|---------|---------|-----------------------|-------|---------|-----------|---------|---------|

| Zustand      | Start/Stopp |       | Ausgang | Zustand | Start/Stopp           |       |         |           |         |         |

|              | 0/0         | 0/1   | 1/0     | 1/1     |                       |       | 0/0     | 0/1       | 1/0     | 1/1     |

| $s_0$        | $s_0$       | $s_0$ | $s_1$   | $s_0$   | 0                     | $s_0$ | $s_0/0$ | $s_0/0$   | $s_1/1$ | $s_0/0$ |

| $s_1$        | $s_1$       | $s_0$ | $s_1$   | $s_0$   | 1                     | $s_1$ | $s_1/1$ | $s_0 / 0$ | $s_1/1$ | $s_0/0$ |

**Moore-Automat**

**Mealy-Automat**

- O In der Automatentabelle werden die Zustände senkrecht und alle möglichen Eingangsbelegungen waagrecht dargestellt

- ⇒ an den Schnittpunkten werden die Folgezustände eingetragen

- **⇒ Moore-Automat: Die Ausgabe wird dem Zustand zugeordnet**

Technische Informatik 2 Stand SS 01 U. Kebschull —

#### **Medvedev- und Moore-Automaten**

- O Auch Moore-Automaten können während des Übergangs Fehlimpulse (Glitches, Hazards) auslösen

- unterschiedliche Laufzeiten in der Schaltung

- ⇒ 01 nach 10 Übergänge der Zustandsübergangsfunktion ohne Änderung des Ausgangswerts

- O Medvedev-Automaten besitzen am Ausgang ein Flipflop

- ⇒ keine Fehlimpulse

- Ausgangswert muss einen Takt früher berechnet werden

| Eingang | Zustand / | Folgezustand | Eingang | Zustand / | Folgezustand |

|---------|-----------|--------------|---------|-----------|--------------|

|         | Ausgang   |              |         | Ausgang   |              |

| -, 1    | S0/ 0     | S0           | -, 1    | S0/ 0     | S0           |

| 0, 0    | S0/ 0     | S0           | 0, 0    | S0/ 0     | S0           |

| 1, 0    | S0/(0)    | S1           | 1, 0    | S0/(1)    | S1           |

| -, 0    | S1/ 1     | S1           | -, 0    | S1/ 1     | S1           |

| -, 1    | S1/(1)    | S0           | -, 1    | S1/(0)    | S0           |

**Moore-Automat**

**Medvedev-Automat**

# 3.3 Analyse und Entwurf von Schaltwerken

#### Grundlegende Realisierung von Automaten

- Asynchrone Realisierung

- ⇒ Zustandsspeicher durch Rückkopplung

- ⇒ es gibt keinen zentralen Takt

- ⇒ die Zustandsspeicher (Flipflops) können zu jedem Zeitpunkt ihren Wert ändern

- **⇒** self-timed

- Synchrone Realisierung

- Rückkopplung nur durch flanken- oder pegelgetriggerte **Flipflops**

- ⇒ die Taktleitungen aller Flipflops sind miteinander verbunden (oder hängen nach einem festen Zeitschema voneinander ab)

- Obwohl asynchrone Realisierungen auch eine gewisse praktische Bedeutung besitzen, werden hier nur synchrone Realisierungen betrachtet

U. Kebschull Technische Informatik 2 Stand SS 01

# 3.3.1 Analyse von Schaltwerken

- O Ein Schaltwerk zu analysieren bedeutet, sein Schaltverhalten durch

- ⇒ eine Zustandstabelle

- ⇒ dessen Schaltfunktion oder

- inen Zustandsgraph zu beschreiben

- **O** Prinzipielles Vorgehen:

- von einem gegebenen Schaltplan werden zunächst die Ausgabe und Übergangsfunktion abgeleitet

- **⇒** ein Anfangszustand wird angenommen

- ight mit den Werten der Eingangsvariablen werden die Folgezustände abgeleitet

- auf diese Weise entstehen die Ablauftabellen

- aus den Ablauftabellen kann der Automatengraph abgeleitet werden

Technische Informatik 2 Stand SS 01

87

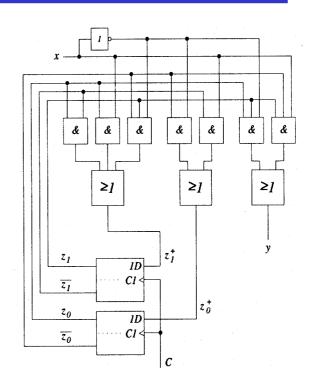

# Beispiel: Ausgangspunkt - der Schaltplan

- GrundlegendeCharakterisierungen

- **⇒** synchrones Schaltwerk

- ⇒ Eingang x und Ausgang y bestehen je aus einer Variablen

- ⇒ das Schaltwerk enthält

2 D-Flipflops

- ⇒ es kann maximal 4 Zustände besitzen

- ⇒ Das Schaltwerk ist ein Mealy-Automat

U. Kebschull

Technische Informatik 2

Stand SS 01

### **Die Schaltfunktion**

- O Aus dem Schaltplan läßt sich ablesen:

- ⇒ für die Übergangsfunktion

$$\begin{split} z_0^+ &= (\overline{z}_0 \wedge \overline{x}) \vee (\overline{z}_1 \wedge x) \\ z_1^+ &= (z_0 \wedge \overline{z}_1) \vee (z_0 \wedge x) \vee (\overline{z}_0 \wedge z_1 \wedge \overline{x}) \end{split}$$

**⇒** für die Ausgabefunktion

$$y = (z_0 \wedge z_1 \wedge \overline{x}) \vee (\overline{z}_0 \wedge z_1 \wedge x)$$

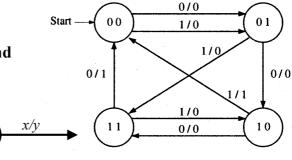

# Die Ablauftabelle und der Automatengraph

- O Aufstellen der Ablauftabelle über die Auswertung der Funktionen für  $z_0, z_1$  und y

- alle Belegungen der Eingangsvariablen

- ⇒ alle Belegungen der Zustandsvariablen

| $z_1$ | $z_0$ | $\boldsymbol{x}$ | $z_1^+$ | $z_0^+$ | $\boldsymbol{y}$ |

|-------|-------|------------------|---------|---------|------------------|

| 0     | 0     | 0                | 0       | 1       | 0                |

| 0     | 0     | 1                | 0       | 1       | 0                |

| 0     | 1     | 0                | 1       | 0       | 0                |

| 0     | 1     | 1                | 1       | 1       | 0                |

| 1     | 0     | 0                | 1       | 1       | 0                |

| 1     | 0     | 1                | 0       | 0       | 1                |

| 1     | 1     | 0                | 0       | 0       | 1                |

| 1     | 1     | 1                | 1       | 0       | 0                |

- Aufstellen des Automatengraphen über die Auswertung der Ablauftabelle

- ⇒ Beschriftung der Zustände und Übergänge nicht vergessen!

U. Kebschull —

Technische Informatik 2 Stand SS 01 91

### 3.3.2 Entwurf von Schaltwerken

- O Prinzipielles Vorgehen:

- **⇒** festlegen der Zustandsmenge

- daraus ergibt sich die Anzahl der erforderlichen Speicherglieder

- **⇒** festlegen des Anfangszustands

- **⇒** Definition der Ein- und Ausgangsvariablen

- ⇒ Darstellung der zeitlichen Zustandsfolge in Form eines Zustandsgraphen

- ⇒ aufstellen der Ablauftabelle

- ⇒ Herleitung der Übergangs- und Ausgabefunktionen

- ⇒ Darstellung der Übergangs- und Ausgabefunktionen in einem KV-Diagramm und Minimierung

- **⇒** Darstellung des Schaltwerks in einem Schaltplan

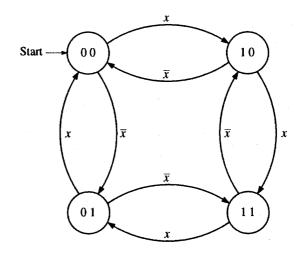

### Beispiel: ein umschaltbarer Zähler

- Es soll ein zweistelliger Gray-Code-Zähler entworfen werden, der sowohl vorwärts als auch rückwärts zählen kann

- O Die Umschaltung der Zählrichtung erfolgt über die Eingangsvariable x

- **⇒ für** *x*=0 **ist die Zählfolge** 00 - 01 - 11 - 10

- **⇒ für** *x*=1 **ist die Zählfolge** 00 - 10 - 11 - 01

- Die Ausgangsvariablen sind identisch mit den Zustandsvariablen, da der Zählerstand angezeigt werden soll

- **➡** Moore-Automat

Automatengraph

U. Kebschull

Technische Informatik 2 Stand SS 01 93

# Ablauftabelle und die Übergangsfunktionen

- O Die Ablauftabelle kann direkt aus dem Automatengraph abgeleitet werden

- $\Rightarrow$  die linke Seite enthält alle Wertekombinationen, die  $z_0$ ,  $z_1$  und x einnehmen können

- ⇒ die rechte Seite enthält die Werte der Folgezustände

- O Aus der Ablauftabelle können die KV-Diagramme für  ${\bf z}_0$  und  ${\bf z}_1$  aufgestellt werden

- Aus den KV-Diagrammen lassen sich die minimierten Übergangsfunktionen ablesen

| $z_1$ | $z_0$ | x | $ z_1^+ $ | $z_0^+$ |

|-------|-------|---|-----------|---------|

| 0     | 0     | 0 | 0         | 1       |

| 0     | 0     | 1 | 1         | 0       |

| 0     | 1     | 0 | 1         | 1       |

| 0     | 1     | 1 | 0         | 0       |

| 1     | 0     | 0 | 0         | 0       |

| 1     | 0     | 1 | 1         | 1       |

| 1     | 1     | 0 | 1         | 0       |

| 1     | 1     | 1 | 0         | 1       |

$$z_1^+ = (\overline{z}_0 \wedge x) \vee (z_0 \wedge \overline{x})$$

$$z_0^+ = (\overline{z}_1 \wedge \overline{x}) \vee (z_1 \wedge x)$$

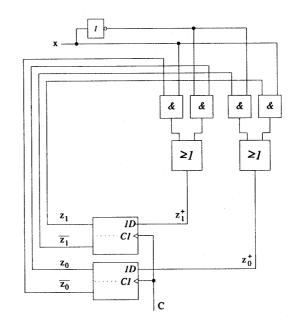

#### Das Schaltwerk

O Die minimierten Übergangsfunktionen können schließlich in einem Schaltplan gezeichnet werden

$$z_0^+ = (\bar{z}_0 \wedge x) \vee (z_0 \wedge \bar{x})$$

$$z_1^+ = (\bar{z}_1 \wedge \bar{x}) \vee (z_1 \wedge x)$$

Stand SS 01 U. Kebschull

# 3.4 Technische Realisierung von Schaltwerken

- O Realisierung mit diskreten Bauelementen

- ⇒ Verknüpfungsglieder

- ⇒ Speicherglieder

- O Die Bauelemente werden entsprechend der Aufgabenstellung durch eine feste Verdrahtung miteinander verbunden

- O Solche Schaltwerksrealisierungen können nur eine feste Aufgabe erfüllen

- ⇒ das Schaltwerk ist nicht flexibel

- ⇒ bei einem Fehler in der Verdrahtung kann keine Korrektur vorgenommen werden

- O Die Bauelemente stehen als integrierte Schaltkreise zur Verfügung

Technische Informatik 2

95

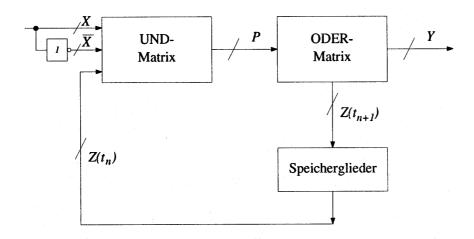

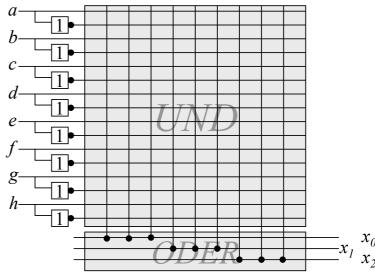

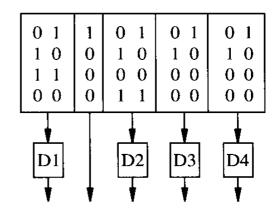

# Realisierung mit einem PLA

- O Programmable Logic Array

- **⇒** technische Realisierung der DMF

- ⇒ UND- und ODER-Matrix sind frei programmierbar

Technische Informatik 2 Stand SS 01 U. Kebschull

# Realisierung mit einem PAL

- O Programmable Array Logic

- **⇒** die ODER-Matrix ist vorgegeben

- ⇒ es steht eine feste Anzahl von Implikanten pro Ausgang zur Verfügung

- ⇒ die UND-Matrix ist programmierbar

U. Kebschull

Technische Informatik 2 Stand SS 01 98

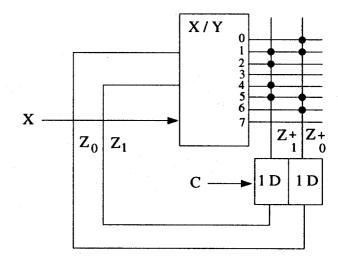

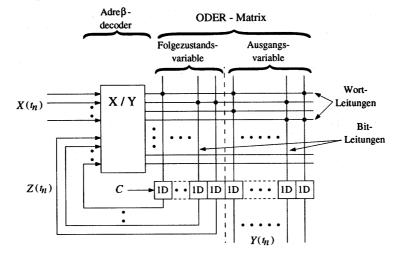

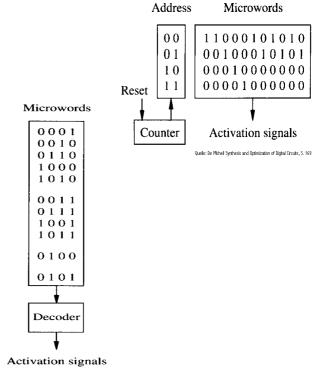

# Realisierung mit einem ROM

- O Technische Realisierung durch ein PROM, EPROM, EEPROM

- O Die UND-Matrix ist durch den Adressdekodierer vorgegeben

- **⇒** alle Minterme sind implementiert

- **⇒** direkte Implementierung der Funktionstabelle

| X | $\mathbf{Z}_1$ | $Z_0$ | $Z_1^+$ | $Z_0^+$ |

|---|----------------|-------|---------|---------|

| 0 | 0              | 0     | 0       | 1       |

| 0 | 0              | 1     | 1       | 1       |

| 0 | 1              | 1     | 1       | 0       |

| 0 | 1              | 0     | 0       | 0       |

| 1 | 0              | 0     | 1       | 0       |

| 1 | 1              | 0     | 1       | 1       |

| 1 | 1              | 1     | 0       | 1       |

| 1 | 0              | 1     | 0       | 0       |

|   |                |       |         |         |

Technische Informatik 2 Stand SS 01 U. Kebschull

# Realisierung mit einem ROM

- O Auch die Ausgabefunktion kann mit einem ROM realisiert werden

- **⇒** Wortorientierung des ROMs wird ausgenutzt

- ⇒ Mikroprogramm

- ⇒ mögliche Implementierung des Steuerwerke in Mikroprozessoren

# 4. Spezielle Schaltnetze und Schaltwerke

- O Für die Implementierung komplexer Schaltungen werden häufig immer wieder kehrende Bausteintypen verwendet

- **O** Typische Schaltnetze sind

- **⇒** Multiplexer/Demultiplexer

- **⇒** Vergleicher

- **⇒** Addierer

- **⇒** Multiplizierer

- Typische Schaltwerke sind

- **⇒** Register

- **⇒** Schieberegister

- ⇒ Zähler

Technische Informatik 2 Stand SS 01 U. Kebschull 101

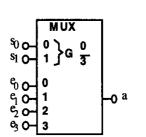

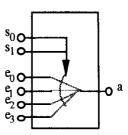

# Multiplexer

- O Mehrere Eingänge, ein Ausgang

- über n Steuerleitungen können 2<sup>n</sup> Eingänge ausgewählt und an den Ausgang durchgeschaltet werden

| S | teuerle        | Ausgang    |                       |

|---|----------------|------------|-----------------------|

|   | s <sub>1</sub> | <b>s</b> 0 | a                     |

|   | 0              | 0          | <b>e</b> <sub>0</sub> |

|   | 0              | 1          | ę                     |

|   | 1              | 0          | $e_2$                 |

|   | . 1            | 1          | e <sub>3</sub>        |

Schaltbild und logisches Verhalten eines 1-aus-4-Multiplexers

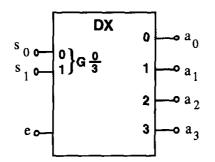

# **Demultiplexer**

O Ein Eingang wird auf einen aus 2<sup>n</sup> Ausgängen durchgeschaltet

| s <sub>1</sub> | s 0 | a <sub>0</sub> | a <sub>1</sub> | a 2              | a 3 |  |

|----------------|-----|----------------|----------------|------------------|-----|--|

| 0              | 0   | e              | 0              | 0<br>0<br>e<br>0 | 0   |  |

| 0              | 1   | 0              | e              | 0                | 0   |  |

| 1              | 0   | 0              | 0              | e                | 0   |  |

| 1              | 1   | 0              | 0              | 0                | e   |  |

|                |     |                |                |                  |     |  |

Schaltbild und logisches Verhalten eines 1-auf-4-Demultiplexers

Technische Informatik 2 Stand SS 01 U. Kebschull 103

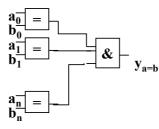

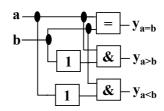

# Vergleicher (Komparatoren)

O Vergleich zweier Zahlen

$$\Rightarrow$$

A=B, AB

O Gleichheit bedeutet, dass alle Bits übereinstimmen

○ 1-Bit Komparator mit Größenvergleich

| a | b | $y_{a>b}$ | $y_{a=b}$ | $y_{a < b}$ |

|---|---|-----------|-----------|-------------|

| 0 | 0 | 0         | 1         | 0           |

| 0 | 1 | 0         | 0         | 1           |

| 1 | 0 | 1         | 0         | 0           |

| 1 | 1 | 0         | 1         | 0           |

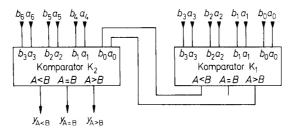

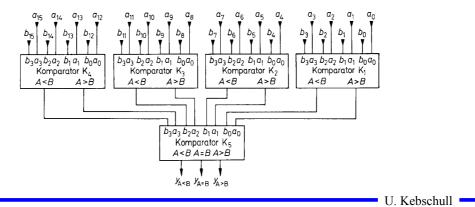

# Komparatoren

#### Serielle Erweiterung

#### Parallele Erweiterung

Technische Informatik 2 Stand SS 01 105

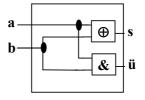

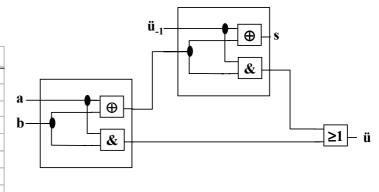

# Addierer

#### Halbaddierer

| а | b | S | ü |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

#### Volladdierer

| s | ü                     |

|---|-----------------------|

| 0 | 0                     |

| 1 | 0                     |

| 1 | 0                     |

| 0 | 1                     |

| 1 | 0                     |

| 0 | 1                     |

| 0 | 1                     |

| 1 | 1                     |

|   | 0<br>1<br>1<br>0<br>1 |

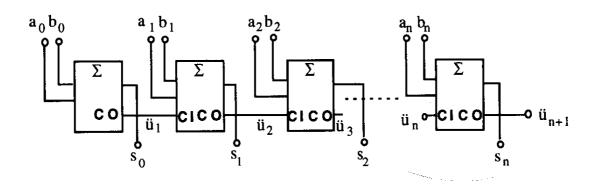

# Addition mit seriellem Übertrag

$\bigcirc$  Der Übertrag des Volladdierers  $\ddot{\mathbf{u}}_{i}$  wird mit  $\mathbf{c}_{i+1}$  verbunden

Technische Informatik 2 Stand SS 01 U. Kebschull 107

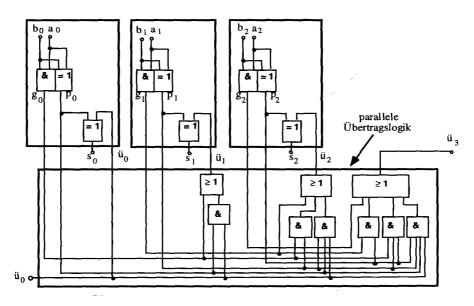

# Addierer mit paralleler Übertragslogik

### O Allgemein:

$$c_i = a_i b_i \vee (a_i \oplus b_i) c_{i-1}$$

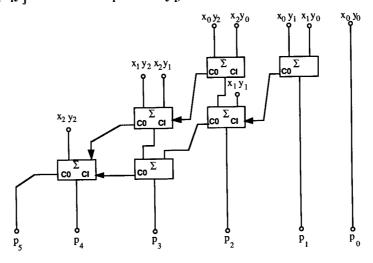

# Multiplizierer

O Parallele Multiplikation durch Addierwerk

$$p = x \cdot y = \left(\sum_{i=0}^{n-1} x_i \cdot 2^i\right) \cdot \left(\sum_{j=0}^{n-1} y_j \cdot 2^j\right) = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} \cdot 2^{i+j} x_i y_j$$

O für n= 3:  $(x_i y_j \text{ steht für } x_i \text{ UND } y_i)$

Technische Informatik 2 Stand SS 01 U. Kebschull 109

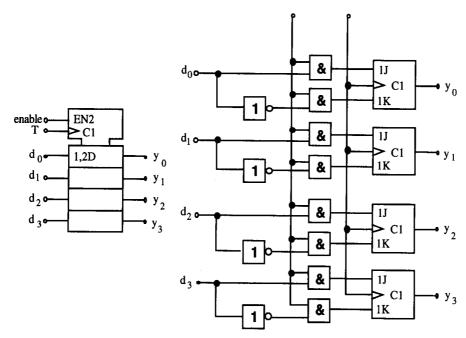

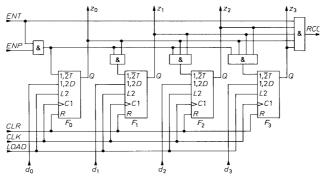

# Register

O Speicherung einer n-stelligen Zahl durch n Flipflops

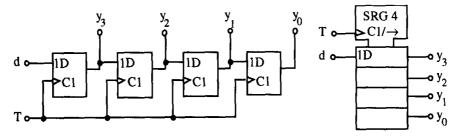

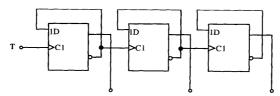

# Schieberegister

- **○** Kette von Flipflops

- Anwendungen:

- **⇒** Serien-Parallel-Wandlung

- **⇒** Parallel-Serien-Wandlung

- **⇒ FIFO oder Stapel-Speicher**

- **⇒** Multiplikation mit 2 oder Division durch 2

- ⇒ mit Rückkopplung zur Erzeugung komplexer Signalfolgen (Sequenzer)

Technische Informatik 2 Stand SS 01 U. Kebschull 111

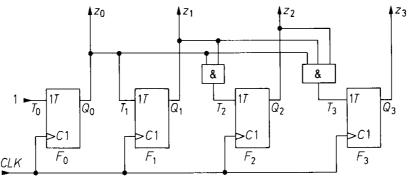

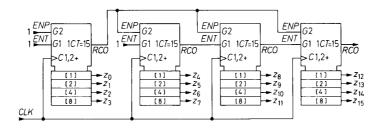

### Zähler

- O Einfacher Dualzähler durch Rückkopplung

- O Asynchroner Ripple Carry Zähler

O Synchroner Dualzähler durch Carry-Look-Ahead-Logik

#### Zähler

#### O Praktische Ausführung eines Zählers

#### O Kaskadierung eines Zählers

Technische Informatik 2 Stand SS 01 U. Kebschull 113

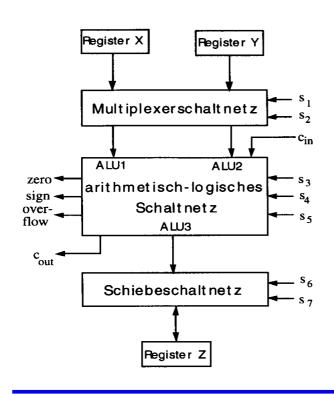

# Aufbau einer ALU

| $\frac{s_1}{0}$  | s <sub>2</sub>   | X<br>X<br>Y           | 0                                      |

|------------------|------------------|-----------------------|----------------------------------------|

| 1                | 1                | Y                     | X                                      |

| $s_3$            | $s_4$            | <b>S</b> <sub>5</sub> | ALU3                                   |

| 0                | 0                | 0                     | ALU1+ALU2+c <sub>in</sub>              |

| 0                | 0                | 1                     | ALU1-ALU2-c <sub>in</sub>              |

| 0                | 1                | 0                     | ALU2-ALU1-c <sub>in</sub>              |

| 0                | 1                | 1                     | ALU1 V ALU2                            |

| 1                | 0                | 0                     | ALU1 ∧ ALU2                            |

| 1                | 0                | 1                     | ALU1 ∧ ALU2                            |

| 1                | 1                | 0                     | ALU1 ↔ ALU2                            |

| 1                | 1                | 1                     | ALU1 ↔ ALU2                            |

| s <sub>6</sub>   | s <sub>7</sub>   |                       | Z                                      |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | A                     | LU3<br>LU3 / 2<br>LU3 * 2<br>speichern |

# **Bauelemente eines Rechnersystems**

- **O** Multiplexer und Demultiplexer zur Steuerung des Datenflusses

- O Zähler für die Programmsteuerung

- O ALU

- **⇒** Register

- **⇒** Addierer

- **⇒** Multiplizierer

- **⇒** Schieberegister

- Speicherzellen

- $\Rightarrow$  RAM

- ⇒ ROM

Technische Informatik 2 Stand SS 01 U. Kebschull 115

### 5 Rechnerarithmetik

- O Die Rechnerarithmetik behandelt

- **⇒** die Darstellung von Zahlen

- ⇒ Verfahren zur Berechnung der vier Grundrechenarten

- ⇒ Schaltungen, die diese Verfahren implementieren

### 5.1 Formale Grundlagen

- O Menschen rechnen und denken im Dezimalsystem

- O Die meisten Rechner verwenden das Dualsystem

- ⇒ man benötigt Verfahren der Konvertierung, die sich algorithmisch umsetzen lassen

#### 7.1.1 Zahlensysteme

- **O** Stellenwertsysteme

- $\Rightarrow$  jeder Position i der Ziffernreihe ist ein Stellenwert zugeordnet welcher der Potenz  $b^i$  der Basis b eines Zahlensystems entspricht  $z_n z_{n-1} ... z_1 z_0 .z_{-1} z_{-2} z_{-m}$

- $\Rightarrow$  der Wert  $X_b$  ergibt sich aus der Summe der Werte aller Einzelstellen

$$X_b = z_n b^n + z_{n-1} b^{n-1} + \dots + z_1 b + z_0 + z_{-1} b^{-1} + z_{-2} b^{-2} + z_{-m} b^{-m} = \sum_{i=-m}^n z_i b^i$$

U. Kebschull

Technische Informatik 2

Stand SS 0

117

# Die wichtigsten Zahlensysteme

| b  | Zahlensystem      | Ziffern                       |

|----|-------------------|-------------------------------|

| 2  | Dualsystem        | 0, 1                          |

| 8  | Oktalsystem       | 0, 1, 2, 3, 4, 5, 6, 7        |

| 10 | Dezimalsystem     | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, |

| 16 | Hexadezimalsystem |                               |

|    |                   | A, B, C, D, E, F              |

- O Dualsystem kann direkt auf 2-wertige Logik umgewandelt werden

- Oktal- und Hexadezimalsystem sind Kurzschreibweisen der Zahlen im Dualsystem

- ⇒ sie lassen sich leicht in Zahlen des Dualsystems umwandeln

# Umwandlung von Dezimalsystem in ein Zahlensystem zur Basis b

- **O** Euklidischer Algorithmus

- ⇒ die einzelnen Ziffern werden sukzessive berechnet

$$Z = z_n b^n + z_{n-1} b^{n-1} + \dots + z_1 b + z_0 + z_{-1} b^{-1} + z_{-2} b^{-2} + z_{-m} b^{-m}$$

=  $y_p b^p + y_{p-1} b^{p-1} + \dots + y_1 b + y_0 + y_{-1} b^{-1} + y_{-2} b^{-2} + y_{-q} b^{-q}$

- **⇒** Algorithmus

- 1. Berechne P gemäß der Ungleichung  $b^{n-1} \le Z < b^n$

- **2. Ermittle**  $y_p$  **und den Rest**  $R_p$  **durch Division von** Z **durch**  $b^p$   $y_p = Z \operatorname{div} b^p$ ;  $R_p = Z \operatorname{mod} b^p$ ;  $y_p = \{0, 1, ..., b\text{-}1\}$

- 3. Wiederhole 2. für i = p-1 und ersetze dabei nach jedem Schritt Z durch  $R_i$ , bis  $R_i=0$  oder bis  $b_i$  klein genug ist

Technische Informatik 2 Stand SS 01 U. Kebschull

119

# **Beispiel**

#### **Umwandlung von** 15741,233<sub>10</sub> ins Hexadezimalsystem

| 1. Schritt | $16^3 \le 15741,233_{10} < 16^4$ | höchste Potenz 16 <sup>3</sup> |

|------------|----------------------------------|--------------------------------|

| 2. Schritt | $15741,233_{10}:16^3=3$          | <b>Rest</b> 3453,233           |

| 3. Schritt | $3453,233:16^2 = D$              | Rest 125,233                   |

| 4. Schritt | 125,233:16=7                     | <b>Rest</b> 13,233             |

| 5. Schritt | 13,233:1=D                       | <b>Rest</b> 0,233              |

| 6. Schritt | $0,233:16^{-1}=3$                | <b>Rest</b> 0,0455             |

| 7. Schritt | $0.0455:16^{-2}=B$               | <b>Rest</b> 0,00253            |

| 8. Schritt | $0.00253:16^{-3}=A$              | Rest 0,000088593               |

| 9. Schritt | $0,000088593:16^{-4}=5$          | Rest 0,000012299               |

|            |                                  | <b>T</b> —Fehler               |

**Ergebnis:**  $15741,233_{10} = 3D7D,3BA5_{16}$

Technische Informatik 2 Stand SS 01 120

#### Umwandlung vom Dezimalsystem in eine Zahl zur Basis b

- O Horner-Schema

- $\Rightarrow$  Eine ganze Zahl  $X_b$  kann auch in der folgenden Form dargestellt werden:

$$X_b = ((...(((y_nb + y_{n-1})b + y_{n-2})b + y_{n-3})b...)b + y_1)b + y_0$$

- $oldsymbol{\circ}$  Die gegebene Dezimalzahl wird sukzessive durch die Basis b dividiert

- $\Rightarrow$  Die jeweiligen ganzzahligen Reste ergeben die Ziffern der Zahl  $X_b$

- ⇒ Reihenfolge: niedrigstwertige zur höchstwertige Stelle

- O Beispiel: Umwandlung von 15741<sub>10</sub> ins Hexadezimalsystem

$3_{10}: 16 = 0$  Rest 3  $(3_{16})$

**Ergebnis:**  $15741_{10} = 3D7D_{16}$

Technische Informatik 2 Stand SS 01 U. Kebschull

121

# Umwandlung des Nachkommateils

ullet Der Nachkommateil einer Zahl  $X_b$  kann in der folgenden Form dargestellt werden

$$Y_b = ((...((y_{-m}b^{-1} + y_{-m+1})b^{-1} + y_{-m+2})b^{-1} + ... + y_{-2})b^{-1} + y_{-1})b^{-1}$$

- O sukzessive Multiplikation des Nachkommateils der Dezimalzahl mit der Basis b des Zielsystems ergibt nacheinander die  $y_{-i}$

- **O** Beispiel: Umwandlung von 0,233<sub>10</sub> ins Hexadezimalsystem

$$0,233 * 16 = 3,728$$

$z_{-1} = 3$

$0,728 * 16 = 11,648$   $z_{-2} = B$

$0,648 * 16 = 10,368$   $z_{-3} = A$

$0,368 * 16 = 5,888$   $z_{-4} = 5$

**Ergebnis:**  $0.233_{10} = 0.3BA5_{16}$

#### Umwandlung einer Zahl zur Basis b ins Dezimalsystem

- Werte der einzelnen Stellen werden mit deren Wertigkeit multipliziert und aufsummiert

- O Beispiel: Umwandlung von 101101,1101 ins Dezimalsystem 101101,1101

$$\begin{array}{rcl}

1 * 2^{-4} & = & 0,0625 \\

0 * 2^{-3} & = & 0 \\

1 * 2^{-2} & = & 0,25 \\

1 * 2^{-1} & = & 0,5 \\

1 * 2^{-0} & = & 1 \\

0 * 2^{1} & = & 0 \\

1 * 2^{2} & = & 4 \\

1 * 2^{3} & = & 8 \\

0 * 2^{4} & = & 0 \\

1 * 2^{5} & = & 32 \\

\hline

& 45,8125_{10}

\end{array}$$

Technische Informatik 2 Stand SS 01 U. Kebschull 123

# Weitere Umwandlungen

- **O** Umwandlung zwischen zwei beliebigen Zahlensystemen

- ⇒ zwei Schritte: Umwandlung ins Dezimalsystem und danach vom Dezimalsystem ins Zielsystem

- O Spezialfall: Eine Basis eine Potenz der anderen Basis

- $\Rightarrow$  Umwandlung erfolgt durch Zusammenfassen der Stellen

- ⇒ Beispiel: Umwandlung von 0110100,110101<sub>2</sub> ins Hexadezimalsystem

#### 5.1.2 Kodierung zur Zahlen- und Zeichendarstellung

- O Die Dezimalzahlen können auch ziffernweise in eine Binärdarstellung überführt werden

- ⇒ um die 10 Ziffern 0 bis 9 darstellen zu können, benötigt man 4 Bit

- ⇒ eine solche 4er-Gruppe wird Tetrade genannt

- ⇒ Pseudotetraden: 6 der 16 Kodierungen stellen keine gültigen Ziffern dar

- O BCD

- **⇒** Binary Coded Decimals

- ⇒ man verwendet das Dualäquivalent der ersten 10 Dualzahlen

- **⇒** Beispiel:

$$8127_{10}\!\!=\!\!1000\ 0001\ 0010\ 0111_{\mathrm{BCD}}\!\!=\!\!1111110111111_2$$

- **⇒** Nachteile der BCD-Kodierung

- höherer Platzbedarf

- aufwändige Implementierung der Rechenoperationen

Technische Informatik 2 Stand SS 01 U. Kebschull 125

# **Gray-Kodierung**

| ○ Einschrittige Kodierung | Dezimalzahl | Gray-Codierung     |

|---------------------------|-------------|--------------------|

| ⇒ bei benachbarten Zahlen | 0           | 0000               |

| ändert sich nur ein       | 1           | 0001               |

| Binärzeichen              | 2           | 0011               |

|                           | 3           | 0010               |

| O Vorteil                 | 4           | 0110               |

| ⇒ keine Hazards bei der   | 5           | 0111               |

| Analog/Digitalwandlung    | 6           | 0101               |

| und bei Abtastern         | 7           | 0100               |

| O Nachteil                | 8           | 1100               |

| ⇒ keine Stellenwertigkeit | 9           | 110 <mark>1</mark> |

| <b>⇒ aufwändige</b>       | 10          | 1111               |

| Rechenoperationen         | 11          | 1110               |

| recencioperationen        | 12          | 1010               |

|                           | 13          | 1011               |

|                           | 14          | 1001               |

|                           | 15          | 1000               |

|                           |             | U. Kebschull       |

Technische Informatik 2 Stand SS 01 126

# Kodierung von Zeichen

- O American Standard Code for Information Interchange (ASCII)

- ⇒ 7 Bit-Kodierung für 128 Zeichen

- ⇒ 2\*26 Zeichen, 10 Ziffern und 32 Kommunikationssteuerzeichen

- **Umlaute und Sonderzeichen sind nicht enthalten**

- **⇒ 8-Bit Erweiterungen unterschiedlicher Computerhersteller**

- ⇒ Andere Verwendung des 8. Bits: Paritätsprüfung

Technische Informatik 2 Stand SS 01 U. Kebschull 127

### **ASCII-Tabelle**

|      | 000 | 001  | 010      | 011 | 100 | 101 | 110 | 111 |

|------|-----|------|----------|-----|-----|-----|-----|-----|

| 0000 | NUL | DLE  | SPACE    | 0   | @   | P   | 1   | p   |

| 0001 | SOH | DC 1 | !        | 1   | A   | Q   | a   | q   |

| 0010 | STX | DC 2 | 11       | 2   | В   | R   | b   | r   |

| 0011 | ETX | DC 3 | #        | 3   | С   | S   | С   | s   |

| 0100 | EOT | DC 4 | \$       | 4   | D   | T   | d   | t   |

| 0101 | ENQ | NAK  | %        | 5   | Е   | U   | e   | u   |

| 0110 | ACK | SYN  | &        | 6   | F   | V   | f   | v   |

| 0111 | BEL | ETB  | <i>'</i> | 7   | G   | W   | g   | w   |

| 1000 | BS  | CAN  | (        | 8   | Н   | X   | h   | х   |

| 1001 | HT  | EM   | )        | 9   | I   | Y   | i   | у   |

| 1010 | LF  | SUB  | *        | ;   | J   | Z   | j   | z   |

| 1011 | VT  | ESC  | +        | ;   | K   | [   | k   | {   |

| 1100 | FF  | FS   | ,        | <   | L   | ١   | 1   | I   |

| 1101 | CR  | GS   | -        | =   | M   | ]   | m   | }   |

| 1110 | so  | RS   |          | >   | N   | ^   | n   | _   |

| 1111 | SI  | US   | /        | ?   | 0   |     | 0   | DEL |

Die höchstwertigen Bits der Kodierung eines Zeichens sind in der Kopfzeile abzulesen, die niederwertigen Bits in der ersten Spalte (Beispiel: A  $\rightarrow$  100 0001<sub>2</sub>).

Technische Informatik 2 Stand SS 01 128

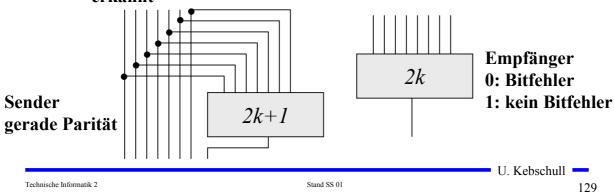

# Paritätsprüfung

- **O** Problem:

- ⇒ Erkennung von Übertragungsfehlern

- O Prinzip:

- ⇒ die 7-Bit Kodierung wird beim Sender so auf 8 Bit ergänzt, dass stets eine gerade (ungerade) Anzahl von Einsen ergänzt

- ⇒ gerade (ungerade) Parität

- ⇒ beim Empfänger wird diese Eigenschaft überprüft

- ⇒ falls bei der Übertragung ein Bitfehler auftritt, wird dieser erkannt

5.1.3 Darstellung negativer Zahlen

- Für die Darstellung von Zahlen in Rechnern werden 4 verschiedene Formate benutzt

- $\Rightarrow$  Darstellung mit Betrag und Vorzeichen

- ⇒ Stellenkomplement (Einerkomplement)

- **⇒** Zweierkomplement

- ⇒ Offset-Dual-Darstellung (Charakteristik)

### Darstellung mit Betrag und Vorzeichen

- O Die erste Stelle der Zahl wird als Vorzeichen benutzt

- ⇒ 0: Die Zahl ist positiv

- ⇒ 1: Die Zahl ist negativ

- O Beispiel:

- $\Rightarrow$  0001 0011 = + 19

- $\Rightarrow$  1001 0011 = 19

- Nachteile dieser Darstellung

- ⇒ bei Addition und Subtraktion müssen die Vorzeichen getrennt betrachtet werden

- ⇒ es gibt 2 Repräsentanten der Zahl 0

- positives und negatives Vorzeichen

Technische Informatik 2 Stand SS 01 U. Kebschull 131

# **Einerkomplement**

- O Jede Ziffer der Binärzahl wird negiert

- ⇒ negative Zahlen werden ebenfalls durch eine 1 an der 1. Stelle gekennzeichnet

- **O** Vorteil:

- ⇒ die 1. Stelle muss bei Addition und Subtraktion nicht gesondert betrachtet werden

- O Beispiel:

- O Nachteil:

- ⇒ es gibt 2 Repräsentanten der Zahl 0:

- 0000 und 1111

# Zweierkomplement

- O Addiert man zum Einerkomplement noch 1 hinzu, dann fallen die beiden Darstellungen der Zahl 0 durch den Überlauf wieder aufeinander

- **⇒ Die Zahl 0** 0000

- **⇒** Einerkomplement 1111

- ⇒ Zweierkomplement 1111 + 0001 = 0000

- Vorteile

- ⇒ das 1. Bit enthält das Vorzeichen

- ⇒ direkte Umwandlung der Zahl Z über die Stellenwertigkeit

**Description**

$$Z = -z_n \cdot 2^n + z_{n-1} \cdot 2^{n-1} + ... + z_1 \cdot 2 + z_0$$

- **⇒** Die Zahl

- $54 = 00110110_2$

- **⇒** mit Vorzeichenbit

- $-54_{10} = 10110110_2$

- **⇒** Einerkomplement

= 11001001<sub>2</sub>

$\Rightarrow$  Zweierkomplement

= 11001010<sub>2</sub>

Technische Informatik 2 Stand SS 01 U. Kebschull 133

# Addition im Zweierkomplement

O Beispiel:

O Beispiel:

#### Charakteristik

- Hauptsächlich in der Darstellung von Exponenten für Gleitkommazahlen

- ⇒ der gesamte Zahlenbereich wird durch die Addition einer Konstanten so nach oben verschoben, dass die kleinste Zahl die Darstellung 0...0 erhält

- O Übersicht der Zahlendarstellungen

| Dez. | Betrag mit Vorz. | Einerkomp.   | Zweierkomp. | Charakteristik |

|------|------------------|--------------|-------------|----------------|

| -4   |                  |              | 100         | 000            |

| -3   | 111              | 100          | 101         | 001            |

| -2   | 110              | 101          | 110         | 010            |

| -1   | 101              | 110          | 111         | 011            |

| 0    | 100 oder 000     | 000 oder 111 | 000         | 100            |

| 1    | 001              | 001          | 001         | 101            |

| 2    | 010              | 010          | 010         | 110            |

| 3    | 011              | 011          | 011         | 111            |

|      |                  |              |             |                |

Technische Informatik 2 Stand SS 01 U. Kebschull 135

### 5.1.4 Fest- und Gleitkommazahlen

| 0 | <b>Darstellung</b> | von | Zahlen | mit | einem | Komma |

|---|--------------------|-----|--------|-----|-------|-------|

|---|--------------------|-----|--------|-----|-------|-------|

Festkommadarstellung

**⇒** Festlegung der Stelle in einem Datenwort

wird heute hardwareseitig nicht mehr eingesetzt

Gleitkommadarstellung

Angabe der Stelle des Kommas in der Zahlendarstellung

$$Z = \pm Mantisse \cdot b^{Exponent}, b \in \{2,16\}$$

- ⇒ negative Zahlen werden meist in Betrag und Vorzeichen dargestellt (kein Zweierkomplement)

- ⇒ sowohl für die Mantisse als auch für die Charakteristik wird eine feste Anzahl von Speicherstellen vorgesehen

# Normalisierte Gleitkommadarstellung

O Eine Gleitkommazahl heißt normalisiert, wenn die folgende Beziehung gilt:

$$\frac{1}{2} \le \text{Mantisse} < 1$$

- ⇒ bei allen Zahlen außer der 0 ist die erste Stelle hinter dem Komma immer 1

- ⇒ legt man für die Zahl 0 ein festes Bitmuster fest, kann man die erste 1 nach dem Komma weglassen

- O Beispiel: Die Zahl 7135<sub>10</sub>

- **⇒** Festkommazahl

0 000 0000 0000 0000 0001 1011 1101 1111<sub>2</sub>

**⇒** Gleitkommadarstellung, normiert

0 100 0110 1 110 1111 0111 1100 0000 0000

⇒ Gleitkommadarstellung, normiert, implizite erste 1

0 100 0110 1 101 1110 1111 1000 0000 0000

Technische Informatik 2 Stand SS 01 U. Kebschull 137

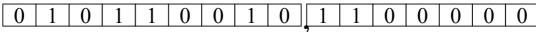

# IEEE Gleitkommadarstellung

- Auch bei gleicher Wortbreite lassen sich unterschiedliche Gleitkommaformate definieren

- ⇒ Normung durch IEEE

- ⇒ einfache Genauigkeit (32 Bit)

31 30 23 22 0 Vz Charakteristik Mantisse

⇒ doppelte Genauigkeit (64 Bit)

63

62

52

51

0

Vz

Charakteristik

Mantisse

- **Digenschaften**

- ⇒ Basis b ist gleich 2

- ⇒ das erste Bit wird implizit zu 1 angenommen, wenn die Charakteristik nicht nur Nullen enthält

- ⇒ Es wird so normalisiert, dass das erste Bit <u>vor</u> dem Komma steht

# IEEE Gleitkommadarstellung

#### **O** Zusammenfassung des 32-bit IEEE-Formats:

| Charakteristik | Zahlenwert                                                    |

|----------------|---------------------------------------------------------------|

| 0              | (-1) <sup>Vz</sup> 0,Mantisse*2 <sup>-126</sup>               |

| 1              | (-1) <sup>Vz</sup> 1,Mantisse*2 <sup>-126</sup>               |