# ناأذ

### UNIVERSITÄT LEIPZIG

#### Institut für Informatik

## Prüfungsaufgaben 2. Klausur

zur Vorlesung WS 2001/2002 und SS 2002

Abt. Technische Informatik

Prof. Dr. Udo Kebschull Dr. Paul Herrmann Dr. Hans-Joachim Lieske

Datum: 11. Februar 2003

Uhrzeit: 14<sup>30</sup>-17<sup>00</sup> Ort: H 19

#### Aufgaben zur Klausur Grundlagen der Technische Informatik 1 und 2

| Name    | Matrikelnummer | Fachrichtung         |

|---------|----------------|----------------------|

| Vorname |                | Immatrikulationsjahr |

|         |                |                      |

|         |                |                      |

|         |                |                      |

| Ergebnisse        |           |           |           |           |       |

|-------------------|-----------|-----------|-----------|-----------|-------|

|                   | Aufgabe 1 | Aufgabe 2 | Aufgabe 3 | Aufgabe 4 | Summe |

| max. Punkte       | 20        | 20        | 20        | 20        | 80    |

| davon<br>erreicht |           |           |           |           |       |

|                   |           |           |           | Note      |       |

Datum/Unterschrift des Korrigierenden (Aufgabe 1/2):

Datum/Unterschrift des Korrigierenden (Aufgabe 2/3):

Hinweise:

Zeitdauer insgesamt 120 Minuten

Zum Bestehen der Klausur sind mindestens 40 Punkte erforderlich.

Zur Klausur Technische Informatik 1 und 2 sind keine Hilfsmittel erlaubt.

**Ausnahme: Taschenrechner**

Ausländer dürfen ein Wörterbuch benutzen.

#### Teil 1 (1. Semester)

#### 1. Aufgabenkomplex - 1. Aufgabe

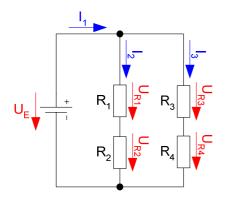

#### Spannungen und Ströme am verzweigten Stromkreis

Eine Konfiguration von Widerständen wird an die Gleichspannung U<sub>E</sub> angeschlossen.

Werte:

$$U_E = 20V$$

$$R_1 = 4,0k\Omega$$

$$R_2 = 6,0k\Omega$$

$$R_3 = 15,0k\Omega$$

$$R_4 = 5,0k\Omega$$

- a) Bestimmen Sie den Ersatzwiderstand  $R_{1/2ers} = R_1 + R_2$ .

- b) Bestimmen Sie den Ersatzwiderstand  $R_{3/4ers} = R_3 + R_4$ .

- c) Bestimmen Sie den Ersatzwiderstand  $R_{1-4ers} = R_{1/2ers} \parallel R_{3/4ers}$ .

- d) Bestimmen Sie den Strom I<sub>1</sub>.

- e) Bestimmen Sie den Strom I<sub>2</sub>.

- f) Bestimmen Sie den Strom I<sub>3</sub>.

- g) Bestimmen Sie die Spannungen  $U_{R1}$  und  $U_{R2}$ .

- h) Bestimmen Sie die Spannungen  $U_{R3}$  und  $U_{R4}$ .

Das Zeichen || bedeutet Parallelschaltung von 2 Widerständen. Die Werte sind ohne die Determinantenmethode auszurechnen.

Formel:

$$U = I \cdot R$$

$$R_1 \parallel R_2 = \left[\frac{1}{R_1} + \frac{1}{R_2}\right]^{-1} = \frac{R_1 \cdot R_2}{R_1 + R_2}$$

Reihenschaltung von Widerständen:

$$R_{ers} = \sum_{k=1}^{n} R_k \quad U_{ges} = \sum_{k=1}^{n} U_k \quad I_1 = I_2 = \dots = I_n$$

Parallelschaltung von Widerständen:

$$\frac{1}{R_{ers}} = \sum_{k=1}^{n} \frac{1}{R_k} \quad I_{ges} = \sum_{k=1}^{n} I_k \quad U_1 = U_2 = \dots = U_n$$

Maßeinheiten:

$$[U] = V [I] = A$$

$[R] = \Omega = \frac{V}{A}$

Alle Werte sind auf 3 Stellen genau zu berechnen

#### 1. Aufgabenkomplex - 2. Aufgabe

#### Logische Gleichungen und logische Schaltungen

Gegeben ist folgende Gleichung:

$$Q = f(x_3, x_2, x_1, x_0) = x_3 x_2 \overline{x}_0 \lor x_3 \overline{x}_2 x_0 \lor \overline{x}_3 \overline{x}_2 x_1 \lor \overline{x}_3 \overline{x}_2 \overline{x}_1$$

- a) Zeichnen Sie die Schaltung streng entsprechend der Gleichung.

- b) Bestimmen Sie die Wertetabelle.

- c) Bestimmen Sie die Minterme und die (kanonisch) disjunktive Normalform  $Q_{\rm KDNF}$ . (Nichtzutreffende Minterme sind in der Tabelle und auch in der Gleichung zu streichen.)

- d) Bestimmen Sie die Maxterme und die (kanonisch) konjunktive Normalform  $Q_{KKNF}$ . (Nichtzutreffende Maxterme sind in der Tabelle und auch in der Gleichung zu streichen.)

- e) Bestimmen Sie die Baumdarstellung und das BDD (Binary Decision Diagram).

- f) Bestimmen Sie das KV-Diagramm und die minimierte Gleichung.

- g) Bestimmen Sie die Gleichung nur mit NAND-Gattern (NAND-Konversion)  $\mathcal{Q}_{\mathit{NAND}}$  .

|                |   | $\mathbf{x}_0$ |    |    |    |   |                       |

|----------------|---|----------------|----|----|----|---|-----------------------|

|                |   | 0              | 1  | 1  | 0  |   |                       |

|                | 0 | 0              | 1  | 5  | 4  | 0 |                       |

| X <sub>3</sub> | 0 | 2              | 3  | 7  | 6  | 1 | <b>X</b> <sub>1</sub> |

|                | 1 | 10             | 11 | 15 | 14 | 1 |                       |

|                | 1 | 8              | 9  | 13 | 12 | 0 |                       |

|                | • | 0              | 0  | 1  | 1  |   |                       |

|                |   |                | X  | 2  |    |   |                       |

|    |   | $\mathbf{x}_0$ |    |    |    |   |                |

|----|---|----------------|----|----|----|---|----------------|

|    |   | 0              | 1  | 1  | 0  |   |                |

|    | 0 | 0              | 1  | 5  | 4  | 0 |                |

| v  | 0 | 2              | 3  | 7  | 6  | 1 | v              |

| X3 | 1 | 10             | 11 | 15 | 14 | 1 | $\mathbf{x}_1$ |

|    | 1 | 8              | 9  | 13 | 12 | 0 |                |

|    | · | 0              | 0  | 1  | 1  |   |                |

|    |   |                | X  | 2  |    |   |                |

#### Name:

#### **Matrikelnummer:**

| Zahl | Eingangsvariablen $x_3, x_2, x_1, x_0$ | Q | Minterme                                                                           | Maxterme                                                                     |

|------|----------------------------------------|---|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 0    | 0000                                   |   | $\overline{x}_3 \wedge \overline{x}_2 \wedge \overline{x}_1 \wedge \overline{x}_0$ | $x_3 \lor x_2 \lor x_1 \lor x_0$                                             |

| 1    | 0001                                   |   | $\overline{x}_3 \wedge \overline{x}_2 \wedge \overline{x}_1 \wedge x_0$            | $x_3 \lor x_2 \lor x_1 \lor \overline{x}_0$                                  |

| 2    | 0010                                   |   | $\overline{x}_3 \wedge \overline{x}_2 \wedge x_1 \wedge \overline{x}_0$            | $x_3 \vee x_2 \vee \overline{x}_1 \vee x_0$                                  |

| 3    | 0011                                   |   | $\overline{x}_3 \wedge \overline{x}_2 \wedge x_1 \wedge x_0$                       | $x_3 \vee x_2 \vee \overline{x}_1 \vee \overline{x}_0$                       |

| 4    | 0100                                   |   | $\overline{x}_3 \wedge x_2 \wedge \overline{x}_1 \wedge \overline{x}_0$            | $x_3 \vee \overline{x}_2 \vee x_1 \vee x_0$                                  |

| 5    | 0101                                   |   | $\overline{x}_3 \wedge x_2 \wedge \overline{x}_1 \wedge x_0$                       | $x_3 \vee \overline{x}_2 \vee x_1 \vee \overline{x}_0$                       |

| 6    | 0110                                   |   | $\overline{x}_3 \wedge x_2 \wedge x_1 \wedge \overline{x}_0$                       | $x_3 \vee \overline{x}_2 \vee \overline{x}_1 \vee x_0$                       |

| 7    | 0111                                   |   | $\overline{x}_3 \wedge x_2 \wedge x_1 \wedge x_0$                                  | $x_3 \vee \overline{x}_2 \vee \overline{x}_1 \vee \overline{x}_0$            |

| 8    | 1000                                   |   | $x_3 \wedge \overline{x}_2 \wedge \overline{x}_1 \wedge \overline{x}_0$            | $\overline{x}_3 \vee x_2 \vee x_1 \vee x_0$                                  |

| 9    | 1001                                   |   | $x_3 \wedge \overline{x}_2 \wedge \overline{x}_1 \wedge x_0$                       | $\overline{x}_3 \vee x_2 \vee x_1 \vee \overline{x}_0$                       |

| 10   | 1010                                   |   | $x_3 \wedge \overline{x}_2 \wedge x_1 \wedge \overline{x}_0$                       | $\overline{x}_3 \vee x_2 \vee \overline{x}_1 \vee x_0$                       |

| 11   | 1011                                   |   | $x_3 \wedge \overline{x}_2 \wedge x_1 \wedge x_0$                                  | $\overline{x}_3 \vee x_2 \vee \overline{x}_1 \vee \overline{x}_0$            |

| 12   | 1100                                   |   | $x_3 \wedge x_2 \wedge \overline{x}_1 \wedge \overline{x}_0$                       | $\overline{x}_3 \vee \overline{x}_2 \vee x_1 \vee x_0$                       |

| 13   | 1101                                   |   | $x_3 \wedge x_2 \wedge \overline{x}_1 \wedge x_0$                                  | $\overline{x}_3 \vee \overline{x}_2 \vee x_1 \vee \overline{x}_0$            |

| 14   | 1110                                   |   | $x_3 \wedge x_2 \wedge x_1 \wedge \overline{x}_0$                                  | $\overline{x}_3 \vee \overline{x}_2 \vee \overline{x}_1 \vee x_0$            |

| 15   | 1111                                   |   | $X_3 \wedge X_2 \wedge X_1 \wedge X_0$                                             | $\overline{x}_3 \vee \overline{x}_2 \vee \overline{x}_1 \vee \overline{x}_0$ |

$$Q_{KDNF} = f(x_3, x_2, x_1, x_0) =$$

$x_3x_2x_1x_0\vee x_3x_2x_1\overline{x}_0\vee x_3x_2\overline{x}_1x_0\vee x_3x_2\overline{x}_1\overline{x}_0\vee x_3\overline{x}_2x_1x_0\vee x_3\overline{x}_2x_1\overline{x}_0\vee x_3\overline{x}_2\overline{x}_1\overline{x}_0\vee x_3\overline{x}_2\overline{x}_1\overline{x}_1\overline{x}_0\vee x_3\overline{x}_2\overline{x}_1\overline{x}_1\overline{x}_0\vee x_3\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}_1\overline{x}$

$$Q_{KKNF} = f(x_3, x_2, x_1, x_0) =$$

$$(x_3 \lor x_2 \lor x_1 \lor x_0) \land (x_3 \lor x_2 \lor x_1 \lor \overline{x}_0) \land (x_3 \lor x_2 \lor \overline{x}_1 \lor x_0) \land (x_3 \lor x_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (x_3 \lor \overline{x}_2 \lor x_1 \lor x_0) \land (x_3 \lor \overline{x}_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (x_3 \lor \overline{x}_2 \lor \overline{x}_1 \lor x_0) \land (x_3 \lor \overline{x}_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (\overline{x}_3 \lor x_2 \lor x_1 \lor x_0) \land (\overline{x}_3 \lor x_2 \lor \overline{x}_1 \lor x_0) \land (\overline{x}_3 \lor x_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (\overline{x}_3 \lor \overline{x}_2 \lor x_1 \lor x_0) \land (\overline{x}_3 \lor \overline{x}_2 \lor \overline{x}_1 \lor \overline{x}_0) \land (\overline{x}_3 \lor \overline{x}_2 \lor x_1 \lor x_0) \land (\overline{x}_3 \lor \overline{x}_2 \lor \overline{x}_1 \lor \overline{x}_0)$$

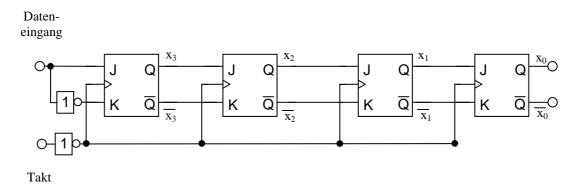

#### 2. Aufgabenkomplex - 3. Aufgabe

#### Flipflops und Schieberegister

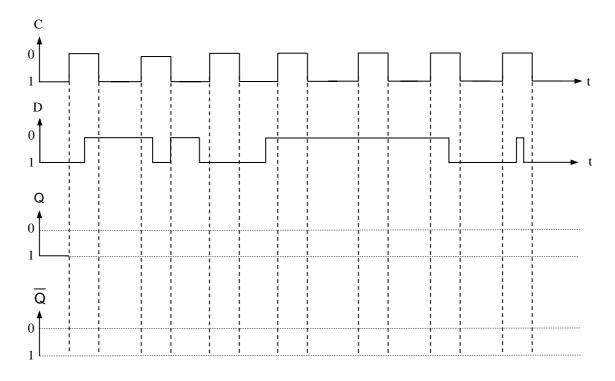

Gegeben sind ein D-Flipflop (mit Zustandssteuerung, kein Master-Slave) sowie dessen zwei Eingangssignale D und C in Form von Impulsdiagrammen:

- a) Geben Sie die Wertetabelle des D-Flipflops an.

- b) Formulieren Sie in einem Satz, wie das Ausgangssignal Q aus den beiden Eingangssignalen entsteht und vervollständigen Sie die Abbildung 1 der Anlage zur Klausur. Dabei sollten Verzögerungszeiten innerhalb des Flipflops vernachlässigt werden (Alle Verzögerungszeiten = 0).

- c) Erläutern Sie die Begriffe Schaltnetz und Schaltwerk. Geben Sie drei typische Schaltnetze sowie drei typische Schaltwerke an.

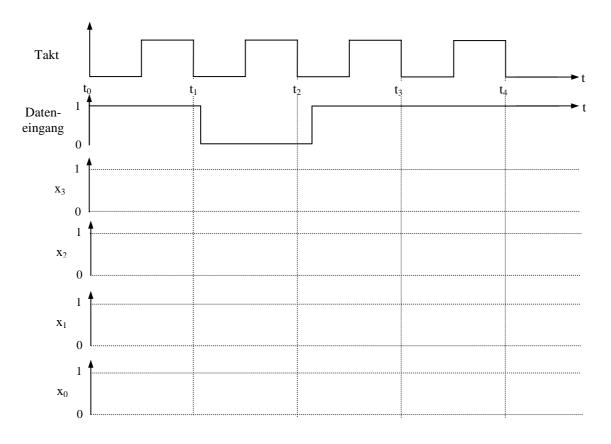

- d) Gegeben ist die folgende Schaltung sowie das zu dieser Schaltung dazugehörige unvollständige Impulsdiagramm (s. Anlage zur Klausur, Abbildung 2):

Handelt es sich bei der gegebenen Schaltung um ein Schaltnetz oder ein Schaltwerk?

Vervollständigen Sie das Impulsdiagramm für die Signale  $x_3$ ,  $x_2$ ,  $x_1$ ,  $x_0$  (Anhang Abbildung 2). Die J-K-Flipflops sollen negativ flankengesteuert sein (aktive Taktflanke ist die High-Low-Flanke). Der Dateneingang liegt zum Zeitpunkt  $t_0$  sowie zu allen Zeitpunkten vor  $t_0$  auf Low-Pegel. Die Flipflops sollen eine Verzögerungszeit größer als Null haben, welche aber so klein sein soll, dass sie auf Ihrem Impulsdiagramm nicht erkennbar ist.

#### 2. Aufgabenkomplex - 4. Aufgabe

#### Additionen in Mikroprozessoren

- a) Eine grundlegende Funktion von Mikroprozessoren ist die Durchführung von Additionen. Erläutern Sie den Unterschied zwischen einem Halbaddierer und einem Volladdierer sowie zeichnen Sie das Schaltbild eines Halbaddierers, das ein Und- sowie ein Exklusiv-Oder-Gatter enthalten soll.

- b) Zwei Halbaddierer kann man nutzen, um einen Volladdierer zu konstruieren. Mehrere Volladdierer lassen sich zu einem Addierer zusammenschalten. Entwerfen Sie einen Addierer, welcher zwei Zahlen im Bereich von 0 bis 15 addieren kann (aus Volladdierern). Wieviele Volladdierer werden für einen solchen Addierer benötigt? Begründen Sie Ihre Antwort. Zeichnen Sie das Schaltbild.

- c) Den einfachsten Prozessor, den Sie kennengelernt haben, ist der Toy-Prozessor. Er kann, wie jeder Prozessor, Additionen ausführen.

Ist er eine Ein-, Zwei- oder Drei-Adress-Maschine? Begründen Sie ihre Antwort.

- d) Schreiben Sie ein Programm für den Toy-Prozessor, das die Inhalte der Speicherstellen \$0 und \$1 addiert sowie das Ergebnis in die Speicherstelle \$2 ablegt.

Ihr Programmkode soll ab Speicherstelle \$3 beginnen und mit einer Endlosschleife beendet werden. Es soll Variablendefinitionen sowie Label enthalten.

Kodieren Sie ihre verwendeten Befehle unter Nutzung des beigelegten Blattes "Befehlssatz" und verwenden Sie passende Kommentare. Schreiben Sie Ihr Programm in der folgenden Form:

| ; Variablen:  |             |             |

|---------------|-------------|-------------|

| <br>; Labels: |             |             |

| <br>\$bc56    | ; BRZ label | ; Kommentar |

Anlage zur 3. Aufgabe

Abbildung 1

Abbildung 2

#### Anlage zur 4. Aufgabe

| Opco         | de Opera    | tion                | Beschreibung                                        |

|--------------|-------------|---------------------|-----------------------------------------------------|

| 0            | STO         | <adresse></adresse> | speichere den ACCU ins RAM an die Adresse           |

| 1            | LDA         | <adresse></adresse> | lade ACCU mit dem Inhalt der Adresse                |

| 2            | BRZ         | <adresse></adresse> | springe nach Adresse, wenn der ACCU Null ist        |

| 3            | ADD         | <adresse></adresse> | addiere den Inhalt der Adresse zum ACCU             |

| 4            | SUB         | <adresse></adresse> | subtrahiere den Inhalt der Adresse vom ACCU         |

| 5            | OR          | <adresse></adresse> | logisches ODER des ACCUS mit dem Inhalt der Adresse |

| 6            | AND         | <adresse></adresse> | logisches UND des ACCUS mit dem Inhalt der Adresse  |

| 7            | XOR         | <adresse></adresse> | logisches ExODER des ACCUS mit dem Inhalt der Adre  |

| 8            | NOT         |                     | logisches NICHT der Bits im ACCU                    |

| 9            | INC         |                     | inkrementiere den ACCU                              |

| 10           | DEC         |                     | dekrementiere den ACCU                              |

| 11           | ZRO         |                     | setze den ACCU auf NULL                             |

| 12           | NOP         |                     | nicht benutzt                                       |

| 13           | NOP         |                     | nicht benutzt                                       |

| 14           | NOP         |                     | nicht benutzt                                       |

| 15           | NOP         |                     | nicht benutzt                                       |

|              |             |                     | II Walankali -                                      |

| echnische lr | nformatik 2 |                     | U. Kebschull Stand SS 02  139                       |